# Agilent U7232B DisplayPort Electrical Performance Compliance Test Application

# **Method of Implementation**

**Agilent Technologies**

# Notices

© Agilent Technologies, Inc. 2007-2011

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Agilent Technologies, Inc. as governed by United States and international copyright laws.

#### **Manual Part Number**

Version 03.00.0000

#### Edition

Seventh edition, March 2011

Available in electronic format only

Agilent Technologies, Inc. 1900 Garden of the Gods Road Colorado Springs, CO 80907 USA

#### Warranty

The material contained in this document is provided "as is," and is subject to being changed, without notice, in future editions. Further, to the maximum extent permitted by applicable law, Agilent disclaims all warranties, either express or implied, with regard to this manual and any information contained herein, including but not limited to the implied warranties of merchantability and fitness for a particular purpose. Agilent shall not be liable for errors or for incidental or consequential damages in connection with the furnishing, use, or performance of this document or of any information contained herein. Should Agilent and the user have a separate written agreement with warranty terms covering the material in this document that conflict with these terms, the warranty terms in the separate agreement shall control.

#### **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

#### **Restricted Rights Legend**

If software is for use in the performance of a U.S. Government prime contract or subcontract, Software is delivered and licensed as "Commercial computer software" as defined in DFAR 252.227-7014 (June 1995), or as a "commercial item" as defined in FAR 2.101(a) or as "Restricted computer software" as defined in FAR 52.227-19 (June 1987) or any equivalent agency regulation or contract clause. Use, duplication or disclosure of Software is subject to Agilent Technologies' standard commercial license terms, and non-DOD Departments and Agencies of the U.S. Government will receive no greater than Restricted Rights as defined in FAR 52.227-19(c)(1-2) (June 1987). U.S. Government users will receive no greater than Limited Rights as defined in FAR 52.227-14 (June 1987) or DFAR 252.227-7015 (b)(2) (November 1995), as applicable in any technical data.

#### **Safety Notices**

A **CAUTION** notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a **CAUTION** notice until the indicated conditions are fully understood and met.

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

## **DisplayPort Automated Testing—At A Glance**

The Agilent U7232B DisplayPort Electrical Performance Compliance Test Application helps you verify DisplayPort Source device under test (DUT) compliance to DisplayPort specifications using an Agilent Infiniium digital storage oscilloscope. The DisplayPort Electrical Performance Compliance Test Application:

- Lets you select individual or multiple tests to run.

- Lets you identify the device being tested and its configuration.

- Shows you how to make oscilloscope connections to the device under test.

- Automatically checks for proper oscilloscope configuration.

- Automatically sets up the oscilloscope for each test.

- Provides detailed information for each test that has been run and lets you specify the thresholds at which marginal or critical warnings appear.

- Creates a printable HTML report of the tests that have been run.

# **NOTE** The tests performed by the DisplayPort Electrical Performance Compliance Test Application are intended to provide a quick check of the electrical health of the DUT. This testing is not a replacement for an exhaustive test validation plan.

Compliance testing measurements are described in Section 3, Source Compliance Tests, in the *DisplayPort-Compliance Test Specification Version 1.2* document, which complies to the *DisplayPort Standards 1.1a* and *1.2*. For more information, see the VESA web site at <u>www.vesa.org</u>.

#### **Required Equipment and Software**

In order to run the DisplayPort automated tests, you need the following equipment and software:

- 80000/90000/90000X series Infiniium Digital Storage Oscilloscope (for Compliance Test Specifications 1.1a and below).

- 90000/90000X series Infinitum Digital Storage Oscilloscope (for Compliance Test Specifications 1.2).

- The minimum version of Infiniium oscilloscope software (see the U7232B test application release notes).

- U7232B DisplayPort Electrical Performance Compliance Test Application.

- W2641A/W2641B DisplayPort Test Point Adapter fixture. Includes four SMA to SMP cables.

- Keyboard, qty = 1, (provided with the Agilent Infiniium oscilloscope).

- Mouse, qty = 1, (provided with the Agilent Infiniium oscilloscope).

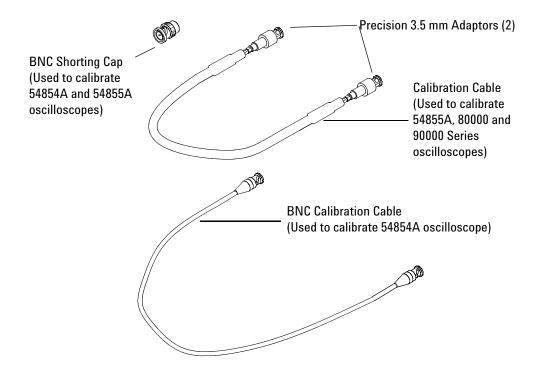

- Precision 3.5 mm BNC to SMA male adapter, Agilent p/n 54855-67604, qty = 2 (provided with the Agilent Infinium oscilloscope).

- Calibration cable (provided with the Infiniium oscilloscopes). Use a good quality 50  $\Omega$  BNC cable for calibrating the oscilloscope.

- E2655A/B probe de-skew fixture.

- E2678A socketed probe.

- E2697A high impedance adapter.

- 1168A or 1169A probes and N5380A SMA probe head.

- U7232B DisplayPort Electrical Performance Compliance Test Application license.

- N5400A EZJIT Plus Jitter Analysis software license.

- N5461A Equalization software license (required for CTS 1.2).

- N5465A InfiniiSim software license (required for CTS 1.2).

In order to run the DisplayPort source automated tests, you need the following additional hardware:

- W2642A DisplayPort Test Controller (DPTC).

- Quantum Data DisplayPort Adapter.

### In This Book

This manual describes the tests that are performed by the DisplayPort Electrical Performance Compliance Test Application in more detail; it contains information from (and refers to) the *DisplayPort Specification Version 1.2*, and it describes how the tests are performed.

- Chapter 1, "Installing the DisplayPort Electrical Performance Compliance Test Application" shows how to install and license the automated test application (if it was purchased separately).

- Chapter 2, "Preparing to Take Measurements" shows how to start the DisplayPort Electrical Performance Compliance Test Application and gives a brief overview of how it is used.

- Chapter 3, "Source Eye Diagram Differential Tests" shows the probing and test procedure of the source data eye diagram differential tests.

- Chapter 4, "Source Total Jitter Differential Tests" shows the probing and test procedure of the source total jitter differential tests.

- Chapter 5, "Source Non-ISI Jitter Differential Tests" shows the probing and test procedure of the source non-isi jitter differential tests.

- Chapter 6, "Source Random Jitter Differential Tests" shows the probing and test procedure of the source random jitter differential tests.

- Chapter 7, "Source Transition Time Differential Tests (Informative)" describes the source rise time and fall time differential tests. These are informative tests.

- Chapter 8, "Source Non Pre-Emphasis Level Differential Tests" describes the source non Pre-Emphasis level differential tests.

- Chapter 9, "Source Overshoot Differential Tests (Informative)" shows the probing and test procedure of the source overshoot differential tests. These are informative tests.

- Chapter 10, "Source Pre-Emphasis Level Differential Tests (Normative & Informative)" shows the probing and test procedure of the source pre-Emphasis differential tests. The Pre-Emphasis Level tests are normative tests whereas Non-Transition Voltage Range Measurements are informative tests.

- Chapter 11, "Source PostCursor 2 Verification Tests (Normative)" shows the probing and test procedure of the source PostCursor 2 verification tests.

- Chapter 12, "Source Inter Pair Skew Differential Tests" shows the probing and test procedure of the source inter pair skew differential tests.

- Chapter 13, "Source Unit Interval Differential Tests (Informative)" describes the source unit interval differential tests. These are informative tests.

- Chapter 14, "Source Main Link Frequency Compliance Differential Tests" shows the probing and test procedure of the source main link frequency compliance differential tests.

- Chapter 15, "Source Spread Spectrum Clocking (SSC) Differential Tests (Normative & Informative)" describes the source spread spectrum clocking (SSC) differential tests. In this SSC test, the Modulation Frequency and Modulation Deviation tests are normative tests whereas Deviation HF Variation tests are informative tests.

- Chapter 16, "Source Rise-Fall Mismatch Single-Ended Tests (Informative)" shows the probing and test procedure of the source rise and fall mismatch single-ended tests.

- Chapter 17, "Source Intra Pair Skew Single-Ended Tests" shows the probing and test procedure of the source intra pair skew single-ended tests.

- Chapter 18, "Source AC Common Mode Noise Single-Ended Tests" shows the probing and test procedure of the source AC common mode noise single-ended tests.

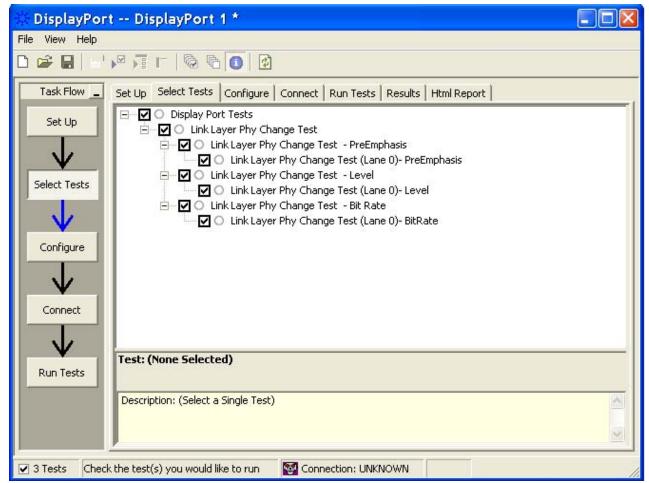

- Chapter 19, "Link Layer Phy Change Tests" describes the link layer phy change tests.

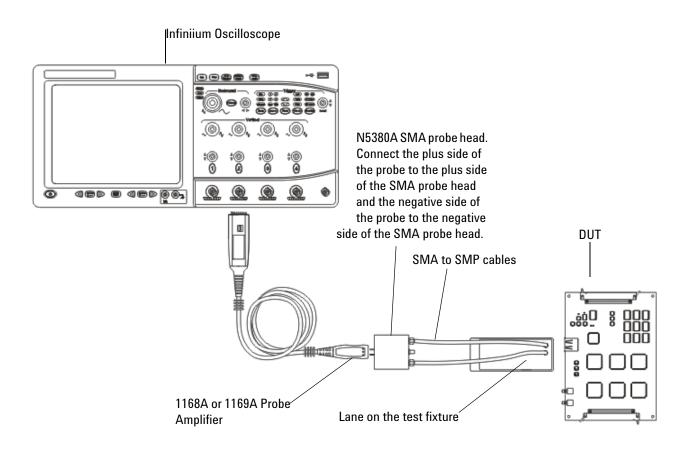

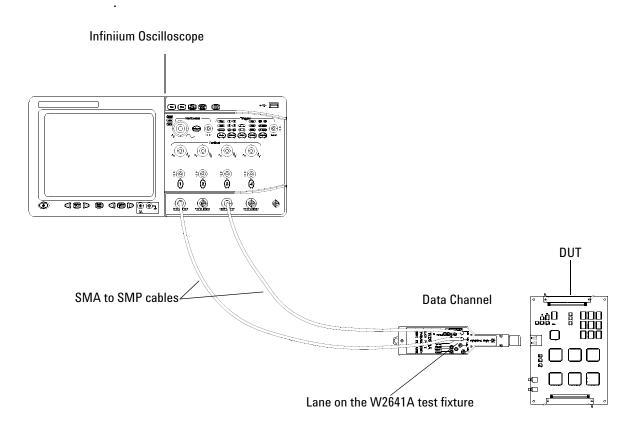

- Chapter 20, "Sink Eye Diagram Tests" shows the probing and test procedure of the sink eye diagram tests.

- Chapter 21, "Sink Total Jitter Tests" contains more information on the sink total jitter tests.

- Chapter 22, "Sink Non-ISI Jitter Tests" shows the probing and test procedure of the sink non-isi jitter tests.

- Chapter 23, "Cable Eye Diagram Tests" shows the probing and test procedure of the cable eye diagram tests.

- Chapter 24, "Cable Total Jitter Tests" contains more information on the cable total jitter tests.

- Chapter 25, "Cable Non-ISI Jitter Tests" contains more information on the cable non-isi jitter tests.

- Chapter 26, "Aux Channel Tests" contains more information on the Aux Channel tests.

- Chapter 27, "Aux Channel Sensitivity Tests" contains more information on the Aux Channel Sensitivity tests.

- Chapter 28, "DP Inrush Tests" contains more information on the DP Inrush tests.

- Chapter 29, "Calibrating the Infinitum Oscilloscope and Probe" describes how to calibrate the oscilloscope in preparation for running the DisplayPort automated tests.

- Chapter 30, "InfiniiMax Probing" describes the 1168A/1169A probe amplifier and probe head recommendations for DisplayPort testing.

#### See Also

- The DisplayPort Electrical Performance Compliance Test Application's online help, which describes:

- Starting the tests.

- Creating or opening a test project.

- Setting up the DisplayPort test environment.

- Setting up the source automated tests with W2642A DPTC.

- Selecting tests.

- Configuring selected tests.

- Connecting the oscilloscope to the DUT.

- Running the tests.

- Viewing the test results.

- Viewing/printing the HTML test report.

- Saving test projects.

- Understanding the HTML report.

# Contents

DisplayPort Automated Testing—At A Glance 3 Required Equipment and Software 3 In This Book 5

See Also 7

#### **1** Installing the DisplayPort Electrical Performance Compliance Test Application

Installing the Software 18

Installing the License Key 19

#### **2** Preparing to Take Measurements

W2641A/W2641B DisplayPort Test Point Adapter Fixture22Acquiring the Test Fixture22W2641A Test Fixture Description22W2641B Test Fixture Description22

Calibrating the Oscilloscope 23

Starting the DisplayPort Electrical Performance Compliance Test Application 24

Online Help Topics 26

#### **3** Source Eye Diagram Differential Tests

Probing for Source Data Eye Diagram Differential Tests 28

Source Eye Diagram Differential Tests 30

Test Procedure 30

- Test Condition 35

- PASS Condition 35

- Test References 37

#### **4** Source Total Jitter Differential Tests

Probing for Source Total Jitter Differential Tests 40

Source Total Jitter Differential Tests 42

- Test Procedure42

- Test Condition 45

- PASS Condition 45

- Test References 46

#### **5** Source Non-ISI Jitter Differential Tests

Probing for Source Non-ISI Jitter Differential Tests 48

Source Non-ISI Jitter Differential Tests 50

Test Procedure 50

Test Condition 53

PASS Condition 53

Test References 54

#### **6** Source Random Jitter Differential Tests

Probing for Source Random Jitter Differential Tests 56

Source Random Jitter Differential Tests 58

Test Procedure 58

Test Condition 61

PASS Condition 61

Test References 61

#### 7 Source Transition Time Differential Tests (Informative)

Probing for Source Transition Time Differential Tests 64

Source Transition Time Differential Tests 66 Test Procedure 66

Test Condition 69

PASS Condition 69

Test References 69

#### 8 Source Non Pre-Emphasis Level Differential Tests

Probing for Source Non Pre-Emphasis Level Differential Tests 72

Source Non Pre-Emphasis Level Test 74

Test Procedure 74

Test Condition 77

PASS Condition 77

Test References 78

#### 9 Source Overshoot Differential Tests (Informative)

Probing for Source Overshoot Differential Tests 80

Source Overshoot Differential Tests 82 Test Procedure 82

Test Condition 85

PASS Condition 85

Test References 85

#### 10 Source Pre-Emphasis Level Differential Tests (Normative & Informative)

Probing for Source Pre-Emphasis Level Differential Tests 88

Source Pre-Emphasis Level Differential Tests 90

Test Procedure91Test Condition94PASS Condition94Test Part97

Test References 95

#### 11 Source PostCursor 2 Verification Tests (Normative)

Probing for Source PostCursor 2 Verification Tests 98

Source PostCursor 2 Verification Tests 100

| Test Procedure  | 101 |

|-----------------|-----|

| Test Condition  | 104 |

| PASS Condition  | 104 |

| Test References | 105 |

#### 12 Source Inter Pair Skew Differential Tests

Probing for Source Inter Pair Skew Differential Tests 108

Source Inter Pair Skew Differential Test 110

Test Procedure110Test Condition113PASS Condition113Test References113

#### **13** Source Unit Interval Differential Tests (Informative)

Probing for Source Unit Interval Differential Tests 116

Source Unit Interval Differential Tests 118

Test Procedure 118

Test Condition 121

PASS Condition 121

Test References 121

#### 14 Source Main Link Frequency Compliance Differential Tests

Probing for Source Main Link Frequency Compliance Differential Tests 124

Source Main Link Frequency Compliance Differential Tests 126

Test Procedure126Test Condition129PASS Condition129Test References129

#### 15 Source Spread Spectrum Clocking (SSC) Differential Tests (Normative & Informative)

Probing for Source Spread Spectrum Clocking (SSC) Differential Tests 132

Source Spread Spectrum Clocking (SSC) Differential Test 134 Spread Spectrum Modulation Frequency (Normative) 134 Spread Spectrum Modulation Deviation (Normative) 134 **Deviation HF Variation (Informative)** 134 Test Procedure 135 SSC Modulation Frequency Test Condition 138 SSC Modulation Deviation Test Condition 138 SSC Deviation HF Variation Test Condition 138 SSC Modulation Frequency PASS Condition 139 SSC Modulation Deviation PASS Condition 139 SSC Deviation HF Variation PASS Condition 139 Test References 139

#### 16 Source Rise-Fall Mismatch Single-Ended Tests (Informative)

Probing for Source Rise-Fall Mismatch Single-Ended Tests 142

Source Rise-Fall Mismatch Single-Ended Tests 143

Test Procedure143Test Condition146PASS Condition146Test References146

# 17 Source Intra Pair Skew Single-Ended Tests

Probing for Source Intra Pair Skew Single-Ended Tests 148

Source Intra Pair Skew Single-Ended Tests 149

Test Procedure149Test Condition152PASS Condition152Test References152

#### 18 Source AC Common Mode Noise Single-Ended Tests

Probing for Source AC Common Mode Noise Single-Ended Tests 154

Source AC Common Mode Noise Single-Ended Test 155

Test Procedure155Test Condition158PASS Condition158Test References158

#### **19 Link Layer Phy Change Tests**

Probing for Link Layer Phy Change Tests 160

Link Layer Phy Change Tests 161 Link Layer Phy Change - Pre-Emphasis 161 Link Layer Phy Change - Level 161 Link Layer Phy Change - Bit Rate 161 Test Procedure 162 **Pre-Emphasis Test Condition** 165 Level Test Condition 165 Bit Rate Test Condition 165 **Pre-Emphasis PASS Condition** 165 Level PASS Condition 165 Bit Rate PASS Condition 166 Test References 166

#### **20** Sink Eye Diagram Tests

Probing for Sink Eye Diagram Tests 168

Sink Eye Diagram Tests 170

Test Procedure 170

PASS Condition 174

Test References 175

#### **21 Sink Total Jitter Tests**

Probing for Sink Total Jitter Tests 178

Sink Total Jitter Tests 180 Test Procedure 180

PASS Condition 184

Test References 184

#### 22 Sink Non-ISI Jitter Tests

Probing for Sink Non-ISI Jitter Tests 186

Sink Non-ISI Jitter Tests 188 Test Procedure 188 PASS Condition 192 Test References 193

#### 23 Cable Eye Diagram Tests

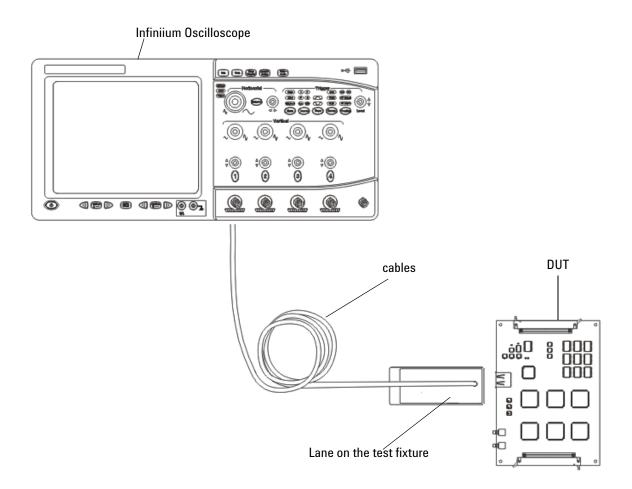

Probing for Cable Eye Diagram Tests 196

Cable Eye Diagram Tests 198

Test Procedure 198

PASS Condition 202

Test References 203

#### 24 Cable Total Jitter Tests

Probing for Cable Total Jitter Tests 206

Cable Total Jitter Tests 208 Test Procedure 208 PASS Condition 212 Test References 212

#### 25 Cable Non-ISI Jitter Tests

Probing for Cable Non-ISI Jitter Tests 214

Cable Non-ISI Jitter Tests 216 Test Procedure 216

PASS Condition 220

Test References 221

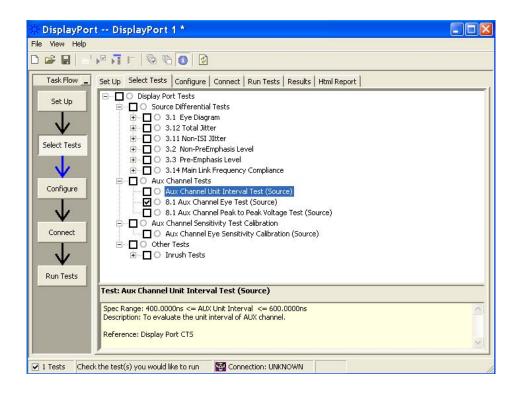

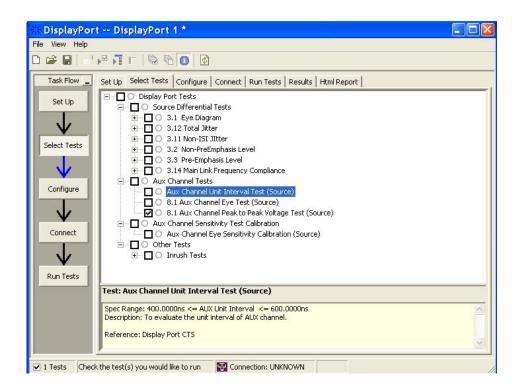

#### **26 Aux Channel Tests**

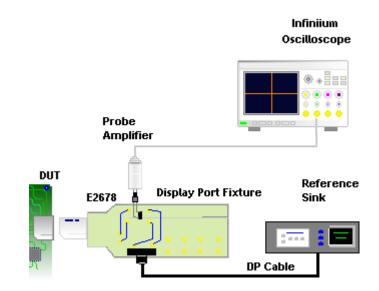

Setting Up for Aux Channel Tests 224

Source Aux Channel Tests 233

Probing/Connection Setup for Source Aux Channel Tests 233 Source Aux Channel Unit Interval Test (Informative) 234 Source Aux Channel Eye Test (Normative) 236 Source Aux Channel Peak-to-Peak Voltage Test (Normative) 238 k Aux Channel Tests 240

Sink Aux Channel Tests 240

Probing/Connection Setup for Sink Aux Channel Tests 240

Sink Aux Channel Unit Interval Test (Informative) 241

Sink Aux Channel Eye Test (Normative) 243

Sink Aux Channel Peak-to-Peak Voltage Test (Normative) 245

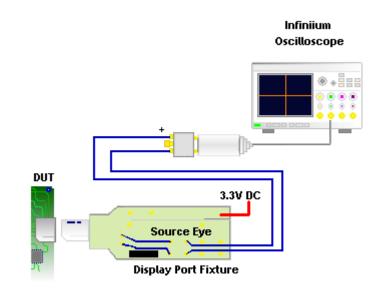

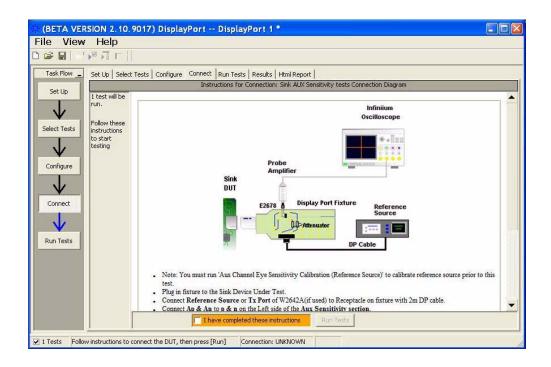

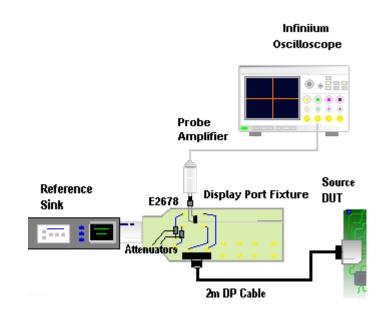

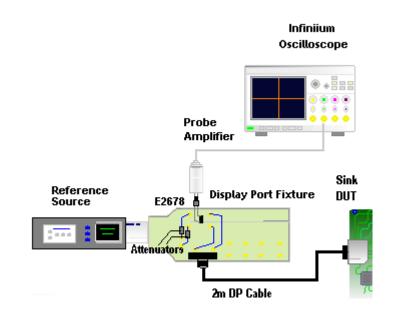

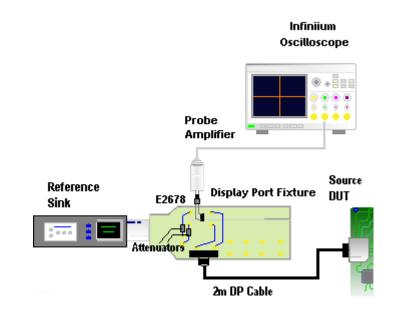

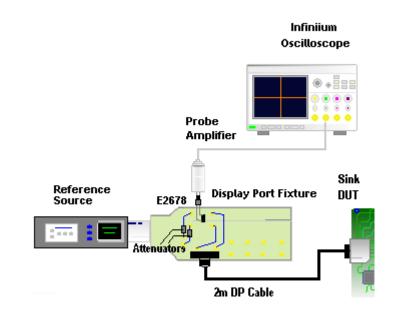

#### 27 Aux Channel Sensitivity Tests

| Setting Up for Aux Channel Sensitivity Tests 248                                                                                                                                                              |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Reference Sink Aux Channel Sensitivity Calibration257Probing/Connection Setup for Aux Channel Sensitivity Calibration2Reference Sink Aux Channel Sensitivity Calibration257                                   | 57 |

| Reference Source Aux Channel Sensitivity Calibration260Probing/Connection Setup for Aux Channel Sensitivity Calibration2Reference Source Aux Channel Sensitivity Calibration260                               | 60 |

| 8.2 Aux Channel Eye Sensitivity Test (Source)263Probing/Connection Setup for Aux Channel Eye Sensitivity Test263Source Aux Channel Eye Sensitivity Test (Normative)263                                        |    |

| <ul> <li>8.2 Aux Channel Eye Sensitivity Test (Sink) 266</li> <li>Probing/Connection Setup for Aux Channel Eye Sensitivity Test 266</li> <li>Sink Aux Channel Eye Sensitivity Test (Normative) 266</li> </ul> |    |

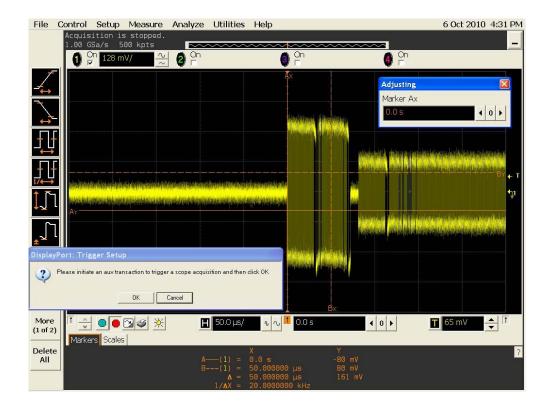

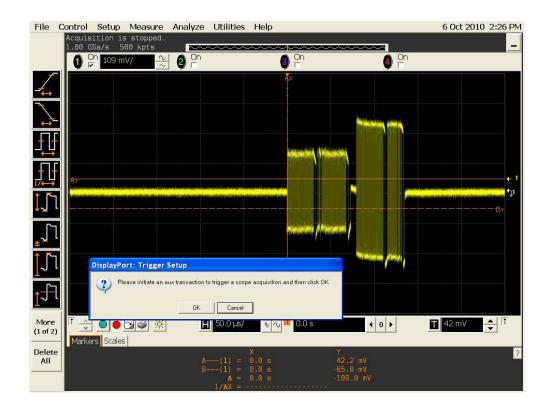

| Initiating Aux Channel Transactions 269<br>Procedure for Initiating Aux Channel Transactions 269                                                                                                              |    |

#### **28 DP Inrush Tests**

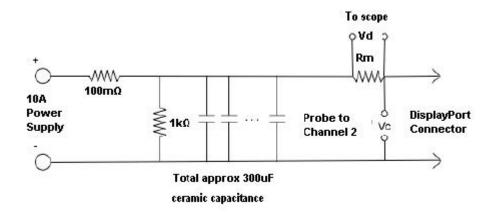

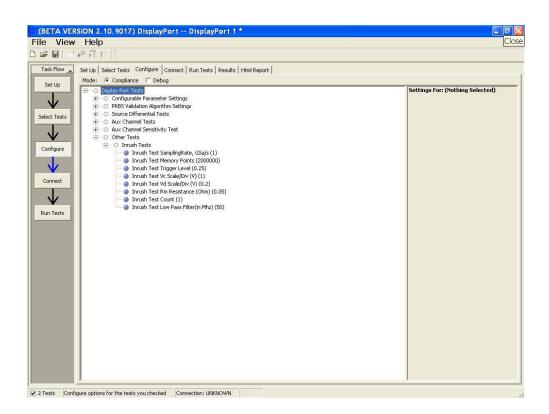

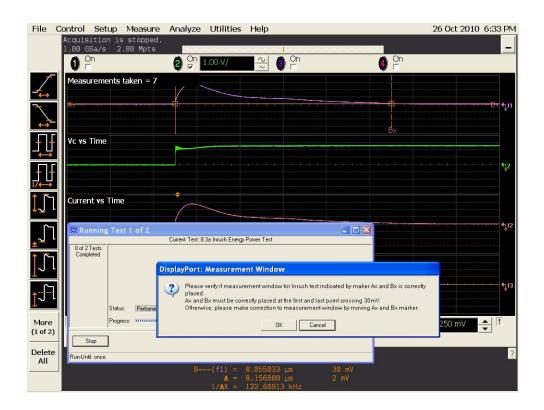

DP Inrush Tests 272 Probing/Connection Setup for DP Inrush Tests 272 Inrush Current Tests (Informative) 272

#### 29 Calibrating the Infiniium Oscilloscope and Probe

| Required Equipment for Calibration 282   |     |

|------------------------------------------|-----|

| Internal Calibration 283                 |     |

| Probe Calibration and De-skew 287        |     |

| SMA probe head Atten/Offset Calibration  | 287 |

| Differential Probe Head Skew Calibration | 291 |

| SMA Probe Head Atten/Offset Calibration  | 293 |

| SMA Probe Head Skew Calibration 297      |     |

#### **30** InfiniiMax Probing

Index

U7232B DisplayPort Electrical Performance Compliance Test Application Method of Implementation

# Installing the DisplayPort Electrical Performance Compliance Test Application

Installing the Software 18 Installing the License Key 19

1

If you purchased the U7232B DisplayPort Electrical Performance Compliance Test Application, you need to install the software and license key.

# **Installing the Software**

- 1 Make sure you have the minimum version of Infiniium oscilloscope software (see the U7232B test application release notes) by choosing **Help>About Infiniium...** from the main menu.

- 2 To obtain the DisplayPort Electrical Performance Compliance Test Application, go to Agilent website: <u>http://www.agilent.com/find/scope-apps-sw</u>.

| Products & Services Technical Support Buy I | dustries About Agilent |  |

|---------------------------------------------|------------------------|--|

| Search: Drivers & Software 💌                | Go                     |  |

| nfiniium Analysis Options                   |                        |  |

| Drivers & Software                          |                        |  |

Figure 1 Agilent website for software Downloads

**3** Search the list on this web page for the link to the U7232B DisplayPort Electrical Performance Compliance Test Application. Click on it and follow the instructions to download and install the application.

# **Installing the License Key**

**1** Request a license code from Agilent by following the instructions on the Entitlement Certificate.

You will need the oscilloscope's "Option ID Number", which you can find in the **Help>About Infiniium...** dialog box.

- 2 After you receive your license code from Agilent, choose Utilities>Install Option License....

- **3** In the Install Option License dialog, enter your license code and click **Install License**.

- **4** Click **OK** in the dialog that tells you to restart the Infiniium oscilloscope application software to complete the license installation.

- 5 Click Close to close the Install Option License dialog.

- 6 Choose File>Exit.

- **7** Restart the Infiniium oscilloscope application to complete the license installation.

1 Installing the DisplayPort Electrical Performance Compliance Test Application

2

U7232B DisplayPort Electrical Performance Compliance Test Application Method of Implementation

# **Preparing to Take Measurements**

W2641A/W2641B DisplayPort Test Point Adapter Fixture 22

Calibrating the Oscilloscope 23

Starting the DisplayPort Electrical Performance Compliance Test Application 24

Online Help Topics 26

Before running the DisplayPort automated tests, you need to acquire the appropriate test fixtures, and you should calibrate the oscilloscope and probe. After the oscilloscope and probe have been calibrated, you are ready to start the DisplayPort Electrical Performance Compliance Test Application and perform the measurements.

# W2641A/W2641B DisplayPort Test Point Adapter Fixture

The W2641A/W2641B test fixture is the Agilent DisplayPort test point adapter fixture that is used for all of the DisplayPort compliance tests.

#### **Acquiring the Test Fixture**

The W2641A/W2641B DisplayPort test point adapter fixture can be acquired from Agilent Technologies.

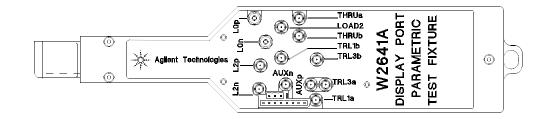

#### W2641A Test Fixture Description

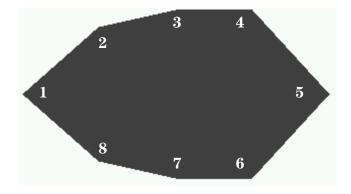

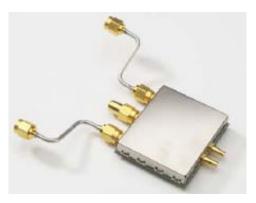

Figure 2 shows the top view of the W2641A test fixture.

Figure 2 W2641A DisplayPort Test Point Adapter Fixture (Top View)

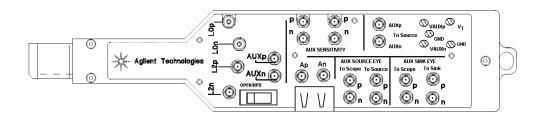

#### W2641B Test Fixture Description

Figure 3 shows the top view of the W2641B test fixture.

Figure 3 W2641B DisplayPort Test Point Adapter Fixture (Top View)

## **Calibrating the Oscilloscope**

If you haven't already calibrated the oscilloscope and probe, see Chapter 29, "Calibrating the Infiniium Oscilloscope and Probe.

**NOTE** If the ambient temperature changes more than 5 degrees Celsius from the calibration temperature, internal calibration should be performed again. The delta between the calibration temperature and the present operating temperature is shown in the Utilities>Calibration menu.

# **NOTE** If you switch cables between channels or other oscilloscopes, it is necessary to perform cable and probe calibration again. Agilent recommends that, once calibration is performed, you label the cables with the channel on which they were calibrated.

#### 2 Preparing to Take Measurements

# **Starting the DisplayPort Electrical Performance Compliance Test Application**

1 From the Infiniium oscilloscope's main menu, choose Analyze>Automated Test Apps>DisplayPort Test.

| Analyze Utilities Help  |                   |

|-------------------------|-------------------|

| Math (FFT and more)     |                   |

| Histogram               |                   |

| Mask Test               |                   |

| Vector Signal Analyzer  |                   |

| M1 Oscilloscope Tools   |                   |

| Jitter                  |                   |

| High Speed Serial Data  |                   |

| Low Speed Serial Data   |                   |

| Automated Test Apps 💦 🕨 | Display Port Test |

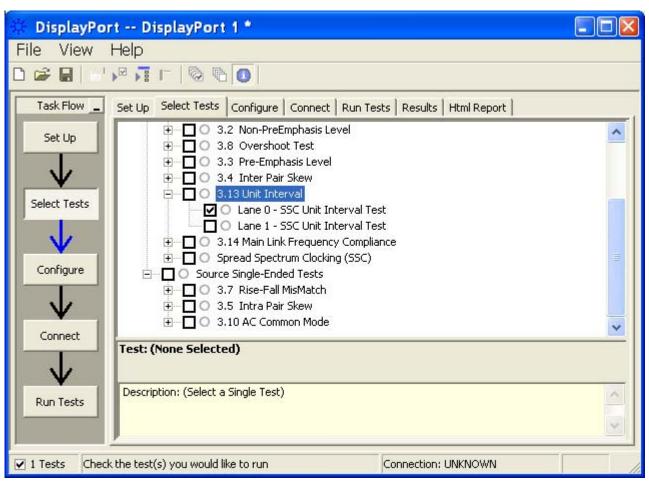

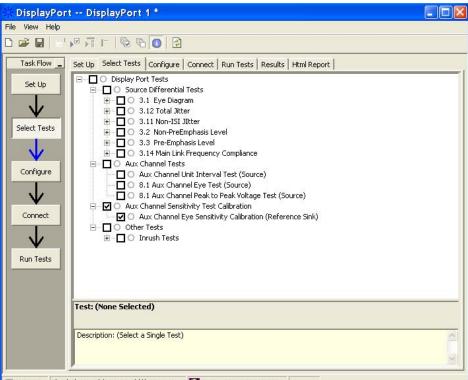

| Task Flow 🔔          | Set Up Select Tests Configure Connect Run Tests Results Ht                                                                                                                                            | ml Report                           |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| Set Up               | DisplayPort Compliance Test Application                                                                                                                                                               | 1                                   |

| ielect Tests         | Source Tests Setup           Test Specification         Test Selection           1.1a <ul> <li>Physical Layer Tests</li> <li>Link Layer Phy Change Tests</li> <li>AUX PHY and Inrush Tests</li> </ul> | Test Setup<br>Test Setup Incomplete |

| Connect<br>Run Tests | DisplayPort Test Controller     AgilentW2642.       Select Script:     s:\scope\apps\dp0250\distrib_CSIDL_PROG       Enable Automation                                                                | Browse<br>Launch GUI                |

Figure 4 The DisplayPort Electrical Performance Compliance Test Application

#### **NOTE** If DisplayPort Test does not appear in the Automated Test Apps menu, the DisplayPort Electrical Performance Compliance Test Application has not been installed (see Chapter 1, "Installing the DisplayPort Electrical Performance Compliance Test Application).

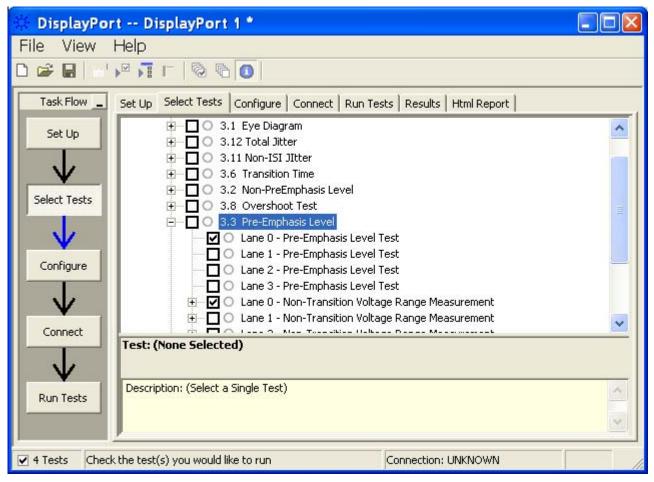

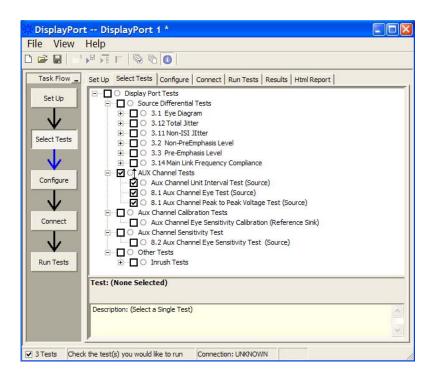

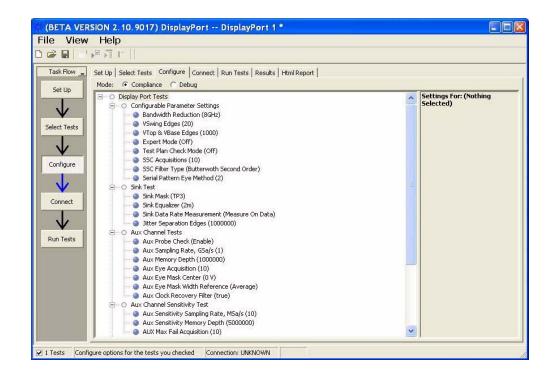

Figure 4 shows the DisplayPort Electrical Performance Compliance Test Application main window. The task flow pane, and the tabs in the main pane, show the steps you take in running the automated tests:

| Set Up       | Lets you select your setup options. Allows you to<br>setup by connection type, device identifier, jitter<br>separation measurements and test fixture type.                                                                                                                         |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Select Tests | Lets you select the tests you want to run. The tests<br>are organized hierarchically, so you can select all<br>tests in a group. After tests are run, status indicators<br>show which tests have passed, failed, or not been<br>run, and there are indicators for the test groups. |

| Configure    | Lets you enter information about the device being<br>tested and configure test parameters (like memory<br>depth). This information appears in the HTML report.                                                                                                                     |

| Connect      | Shows you how to connect the oscilloscope to the device under test for the tests to be run.                                                                                                                                                                                        |

| Run Tests    | Starts the automated tests. If the connections to the device under test need to be changed while multiple tests are running, the tests pause, show you how to change the connection, and wait for you to confirm that the connections have been changed before continuing.         |

| Results      | Contains more detailed information about the tests<br>that have been run. You can change the thresholds at<br>which marginal or critical warnings appear.                                                                                                                          |

| HTML Report  | Shows a compliance test report that can be printed.                                                                                                                                                                                                                                |

#### NOTE

When you close the DisplayPort application, each channel's probe is configured as single-ended or differential depending on the last DisplayPort test that was run.

#### **2** Preparing to Take Measurements

## **Online Help Topics**

For information on using the DisplayPort Electrical Performance Compliance Test Application, see the online help (which you can access by choosing **Help>Contents**... from the application's main menu).

The DisplayPort Electrical Performance Compliance Test Application's online help describes:

- Running the Compliance Test Application on a second monitor.

- Starting the DisplayPort Electrical Performance Compliance Test Application.

- To view or minimize the task flow pane.

- To view or hide the toolbar.

- Creating or opening a test project.

- Setting up DisplayPort test environment.

- Setting up DisplayPort automated tests with W2642A DPTC.

- Selecting the tests.

- Configuring selected tests.

- Connecting the oscilloscope to the Device Under Test (DUT).

- Running the tests.

- Viewing test results.

- To show reference images and flash mask hits.

- To change the display settings.

- To change the margin thresholds and report trial display.

- To change the auto-recovery option.

- Viewing or printing the HTML test report.

- Saving the test projects.

- Understanding the DisplayPort HTML report.

3

U7232B DisplayPort Electrical Performance Compliance Test Application Method of Implementation

# **Source Eye Diagram Differential Tests**

Probing for Source Data Eye Diagram Differential Tests 28 Source Eye Diagram Differential Tests 30

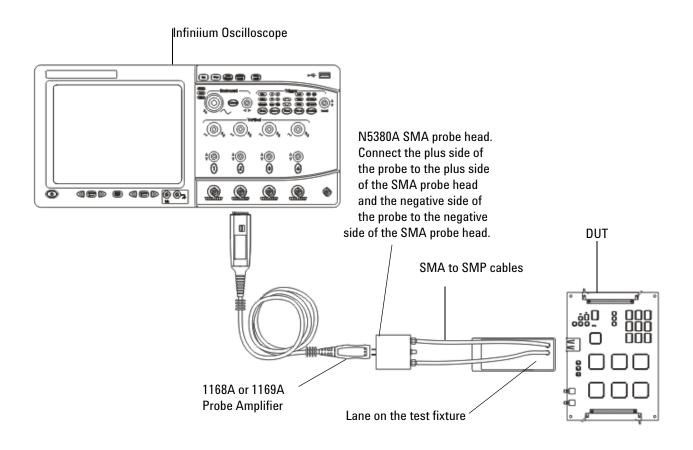

This section provides the guidelines for source eye diagram differential tests using an Agilent Infiniium oscilloscope, 1168A or 1169A probes, and the DisplayPort Electrical Performance Compliance Test Application.

#### **3** Source Eye Diagram Differential Tests

## **Probing for Source Data Eye Diagram Differential Tests**

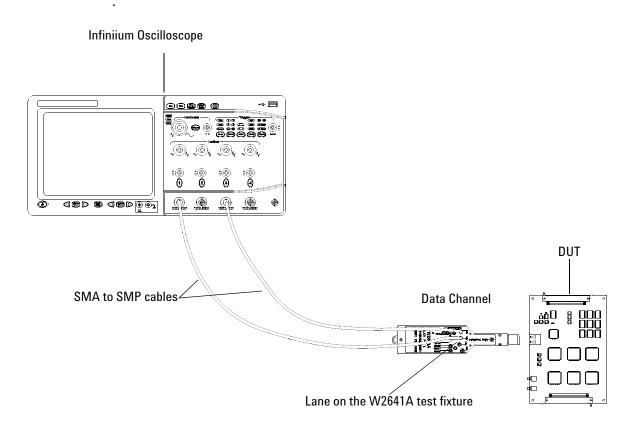

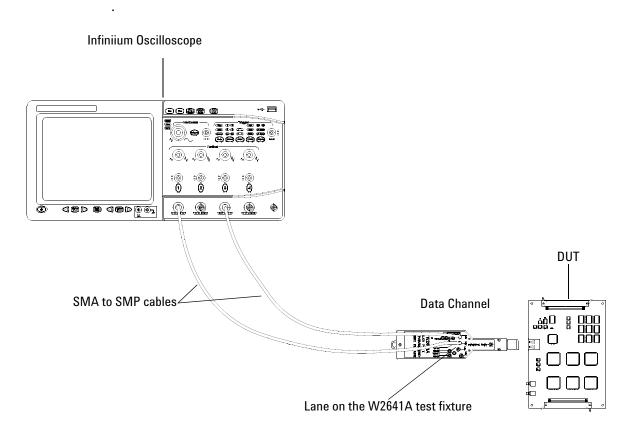

When performing the data eye diagram test, the DisplayPort Electrical Performance Compliance Test Application will prompt you to make the proper connections. Your DisplayPort test environment setup on the Set Up tab must match the physical connection.

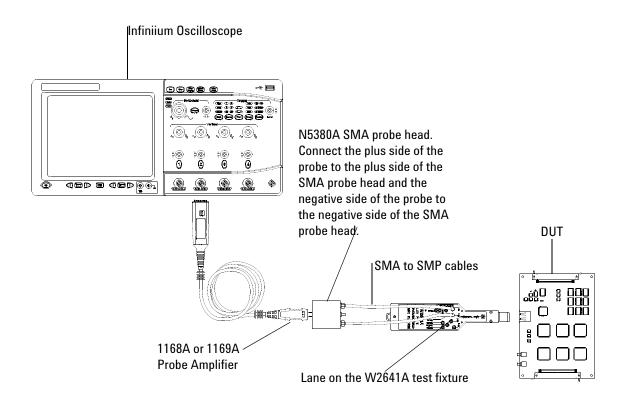

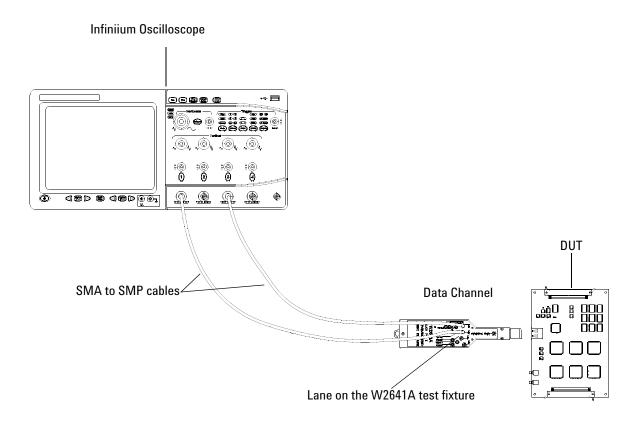

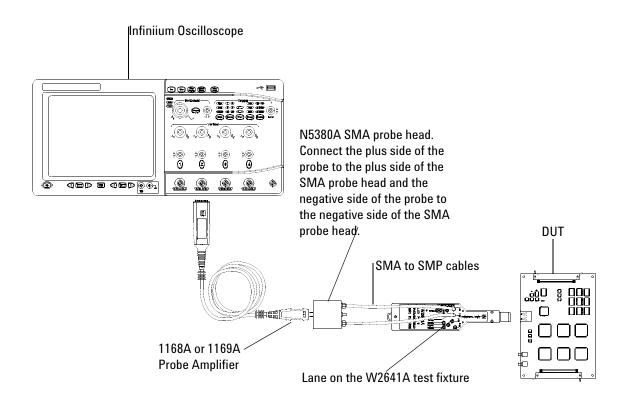

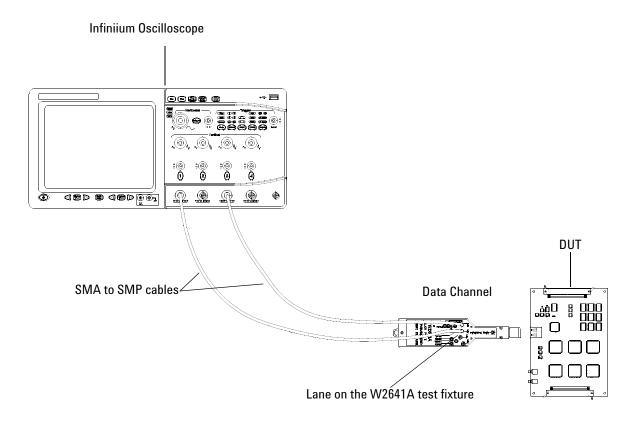

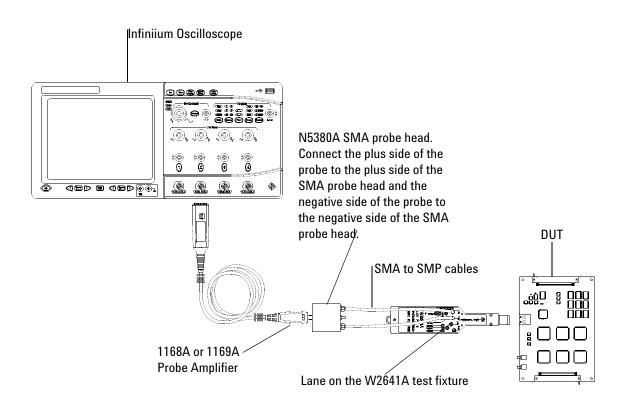

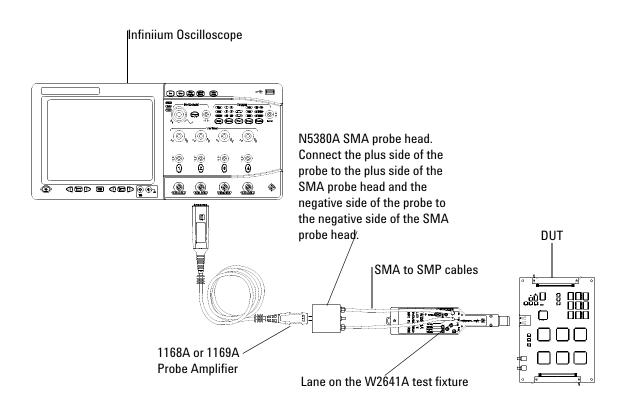

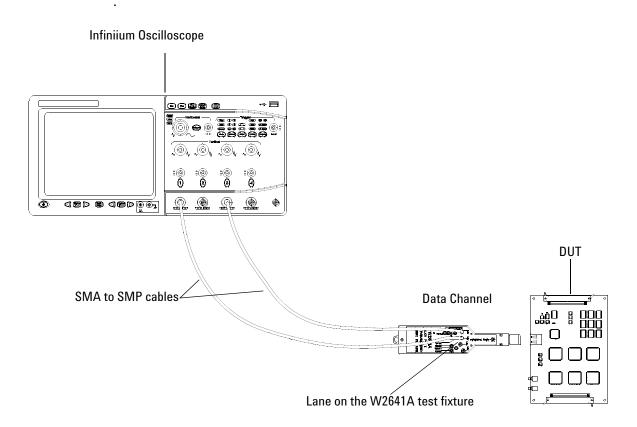

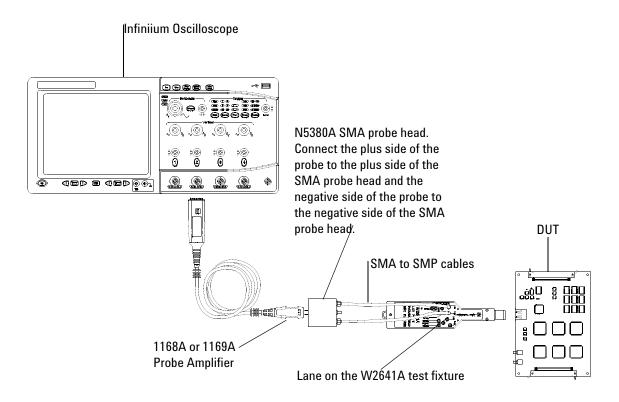

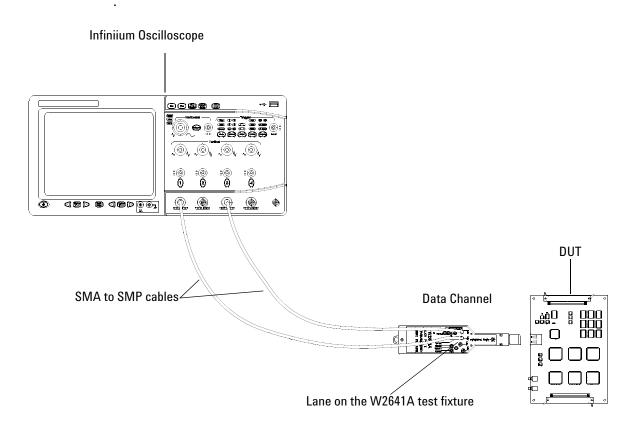

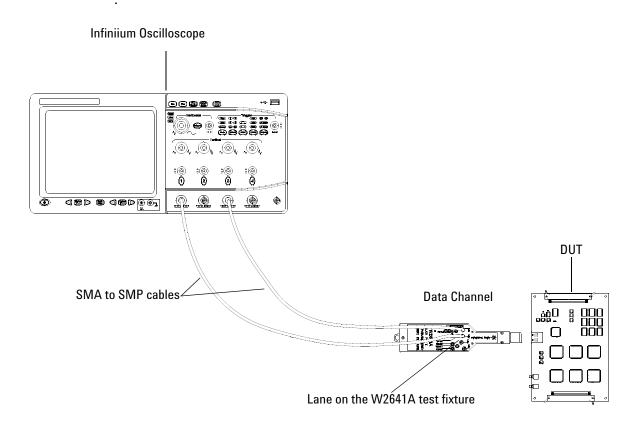

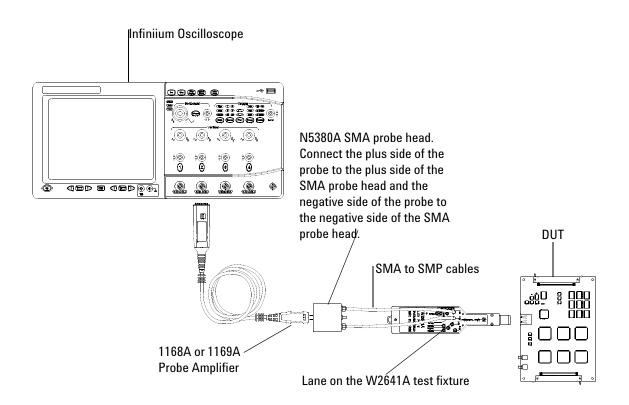

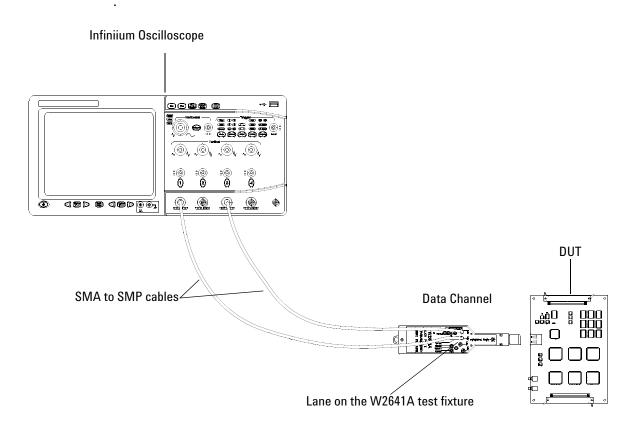

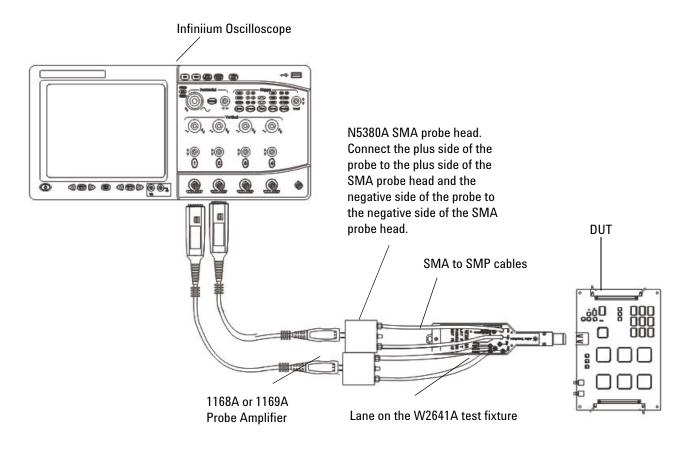

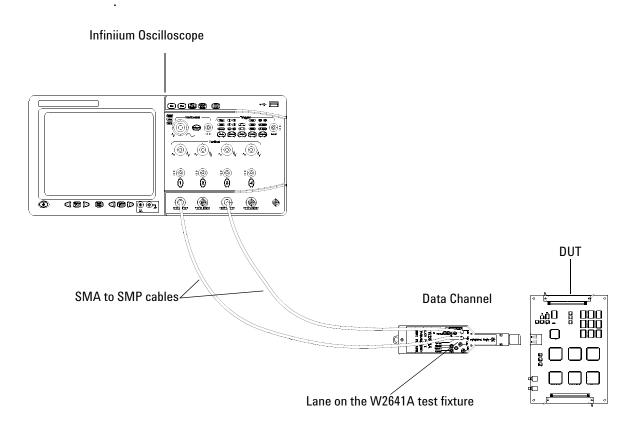

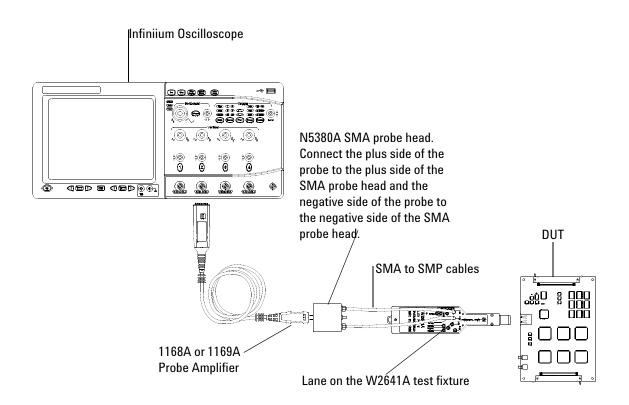

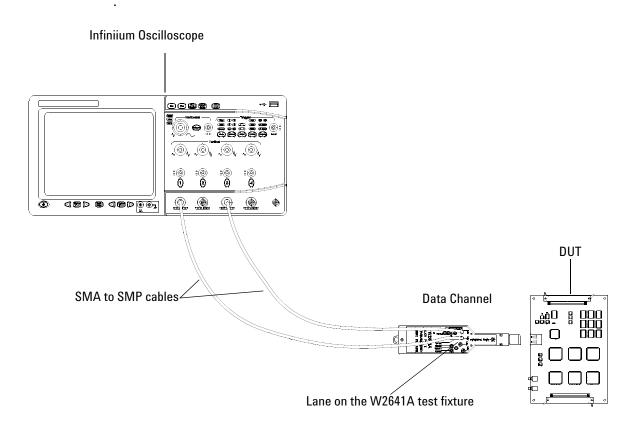

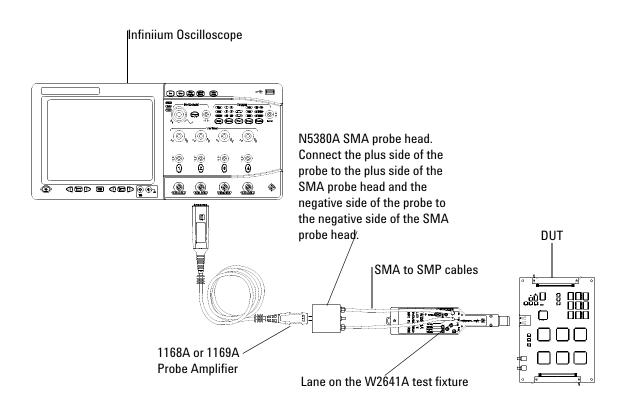

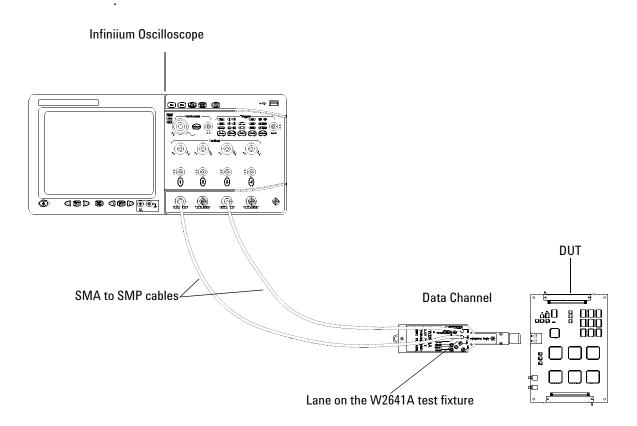

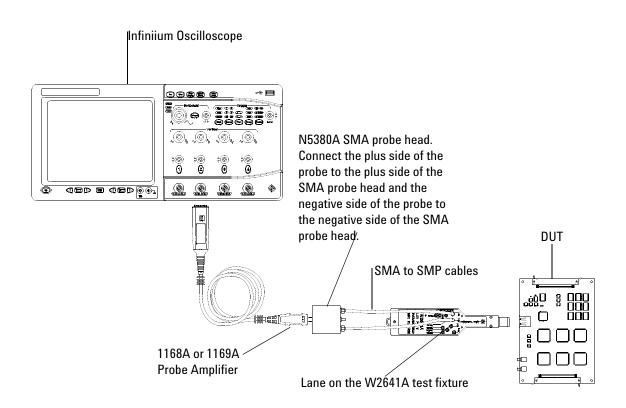

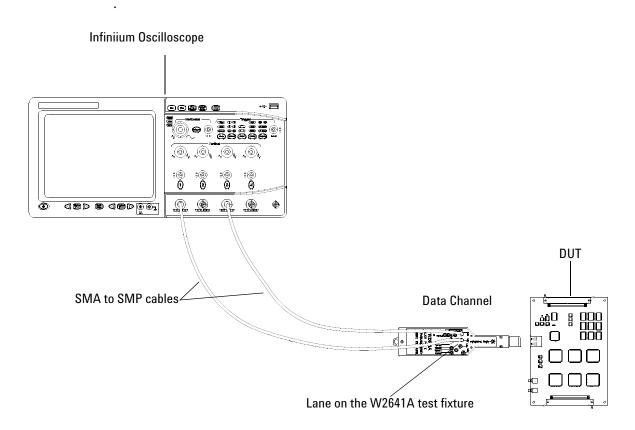

Figure 5 and Figure 6 show a physical connection for making differential and single-ended connections.

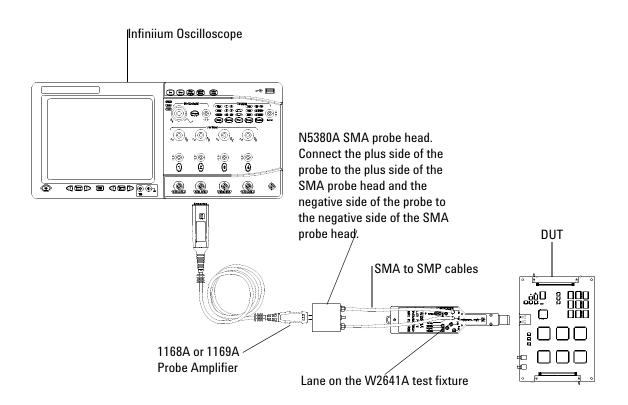

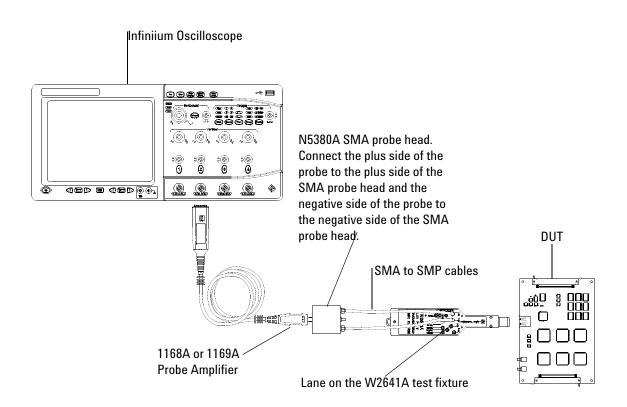

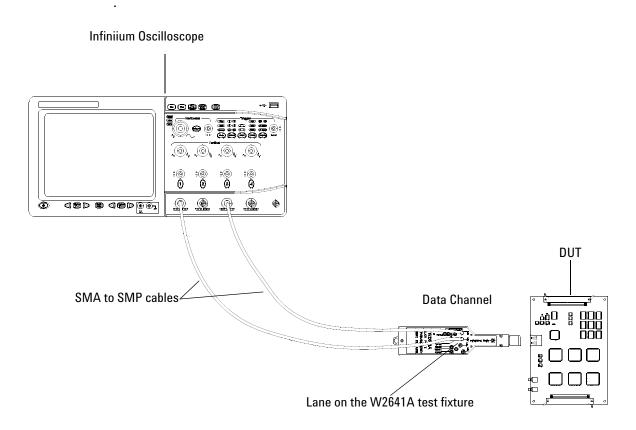

**Figure 5** Probing for Differential Tests - Data Eye Diagram Tests (Single Connection with W2641A DisplayPort Test Fixture)

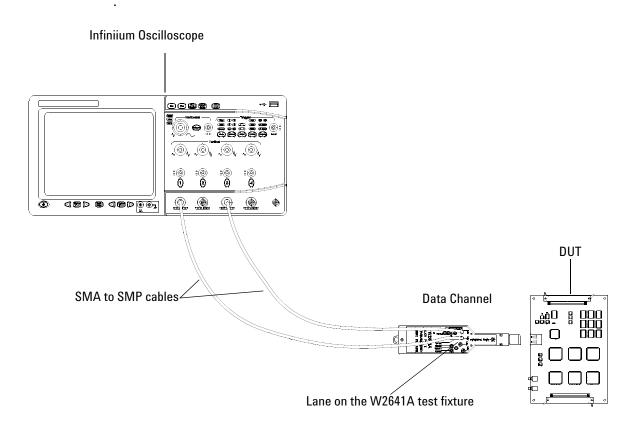

**Figure 6** Differential Measurement Setup Using Two Single Ended Connections - Data Eye Diagram Tests (A Minus B Configuration)

You can use any oscilloscope channel and connect it to any lane test point. You select the channels used for testing lanes in the Set Up tab of the DisplayPort Electrical Performance Compliance Test Application.

The data lanes and channels shown in the previous figures are just examples. You can choose any desired data lane and channel that you want.

For more information on the 1168A or 1169A probe amplifiers and differential probe heads, see Chapter 30, "InfiniiMax Probing," starting on page 299.

# **Source Eye Diagram Differential Tests**

The eye diagram test provides a visual evaluation of the amplitude and timing variations of the waveform with the overall objective of obtaining a specified bit error rate in transmitted data. The test must use a PRBS 7 test pattern at all voltage levels (for Compliance Test Specifications 1.1a and below) or an 8b10b test pattern (for Compliance Test Specifications 1.2). The test should be performed without pre-Emphasis.

The source eye diagram performance provides the best visual assessment of interoperability potential by showing amplitude and timing minimum and maximum values.

#### **Test Procedure**

- 1 Start the automated testing application as described in "Starting the DisplayPort Electrical Performance Compliance Test Application" on page 24.

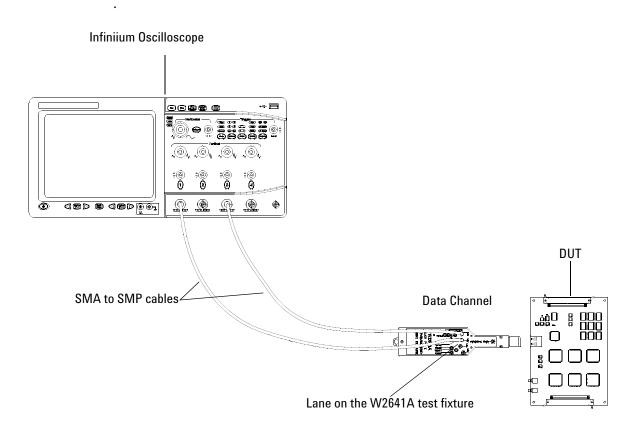

- **2** Connect the W2641A test fixture or other appropriate fixture to the device under test (DUT).

- **3** If you are using one connection, connect the probe to one channel. If you are using two connections, connect the two probes to two channels of the oscilloscope. If you are using four connections, connect the four probes to four channels of the oscilloscope.

- **4** Connect the SMA to SMP cable to the SMA probe head of one of the probes and to the data lane connector on the W2641A fixture that you want to test.

- **5** Connect the other SMA to SMP cable to the other SMA probe head and to the data lane on the W2641A test fixture that you want to test.

| ask Flow 🔔 Set Up | Select Tests Configu                    | re   Connect   Run Tests   Results   Htr                                          | ml Report  |

|-------------------|-----------------------------------------|-----------------------------------------------------------------------------------|------------|

| Set Up Displ      | ayPort Compliance                       | e Test Application                                                                |            |

|                   | rce Tests Setup                         | Test Selection                                                                    | 1          |

| elect lests       | 1.1a                                    | Physical Layer Tests     Link Layer Phy Change Tests     AUX PHY and Inrush Tests | Test Setup |

| onnect Disp       | ·                                       | oller AgilentW2642.                                                               | Browse     |

|                   | ect Script: s:\sco<br>Inable Automation | ppe\apps\dp0250\distrib_CSIDL_PROG                                                | Launch GUI |

6 In the DisplayPort Compliance Test Application, click the Set Up tab.

Figure 7 Set Up for Data Eye Pattern Differential Tests

| Device ID<br>Operator ID              | - Comments                                                                                                   |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Project ID                            |                                                                                                              |

| Device Type:                          | Description                                                                                                  |

| Source  Test Type: Differential Tests | Device Type:<br>DisplayPort compliance application<br>defines three categories for the<br>type of device(s). |

|                                       |                                                                                                              |

|                                       |                                                                                                              |

|                                       |                                                                                                              |

Figure 8 Test Type Set Up for Data Eye Pattern Differential Tests

7 Set the Device ID, Operator ID, Project ID, Test Type, DUT Definition Settings, Fixture Type, Connection Type and Number of Channels according to the type of testing being done.

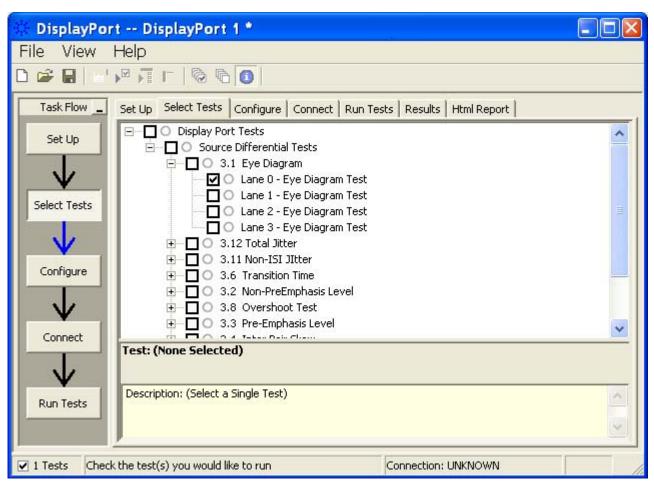

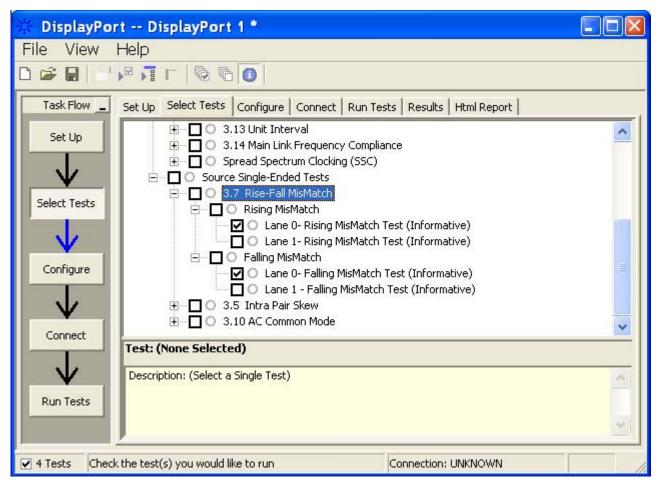

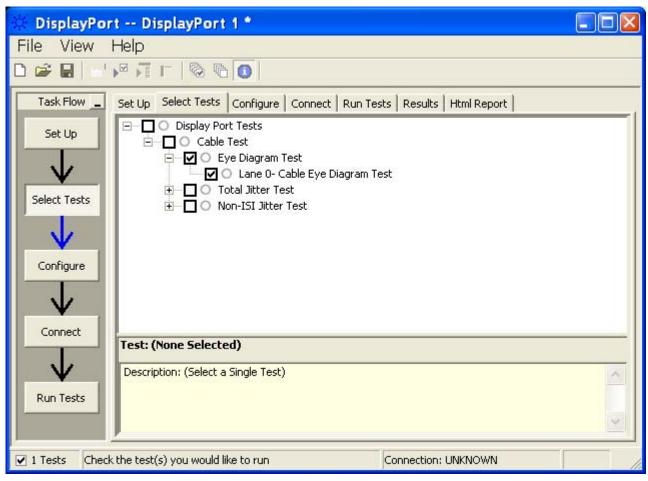

Navigate to the Eye Diagram - Lane # - Eye Diagram Test where # is the lane number to be tested.

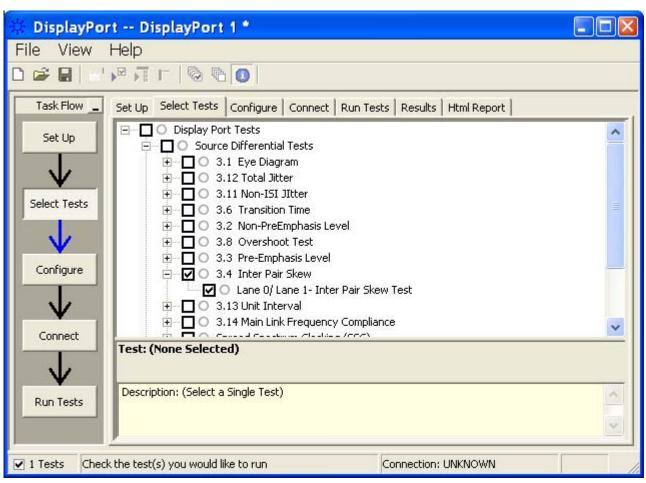

Figure 9 Selecting Data Eye Pattern Differential Tests

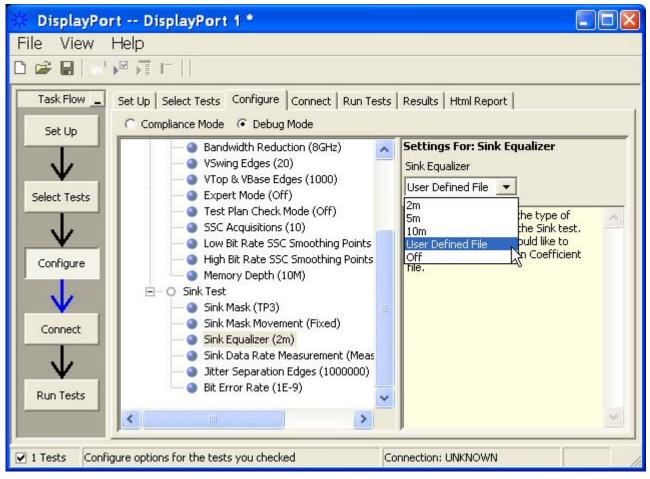

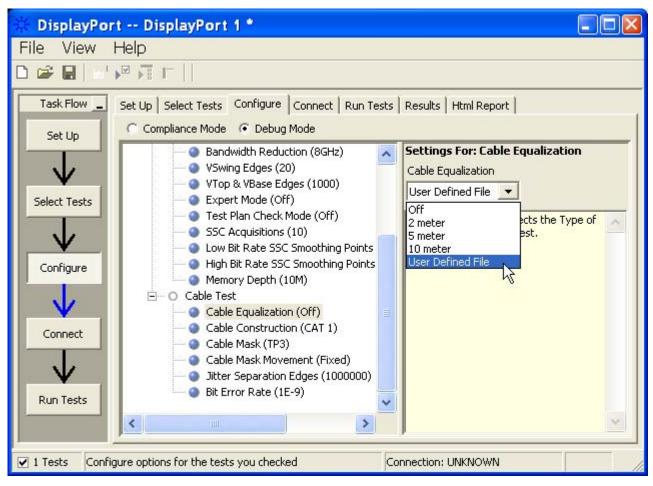

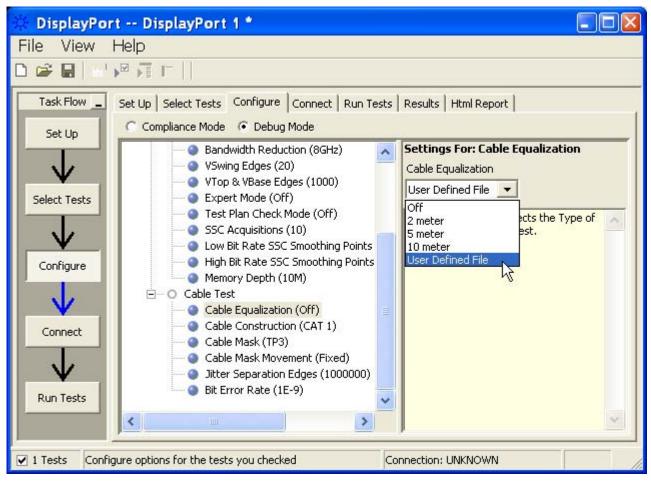

8 Follow the DisplayPort Electrical Performance Compliance Test Application's task flow to set up configuration options (see Table 1), run the test and view the test results. Options may vary depending on selected mode: Compliance Mode or Debug Mode.

## **3** Source Eye Diagram Differential Tests

### Table 1 Test Configuration Options

| Configuration Option             | Description                                                                                                                                                                                                                                                                                                 |  |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Clock Recovery Settings          |                                                                                                                                                                                                                                                                                                             |  |

| Clock Recovery Order             | Set either a second order PLL or a first order PLL method to recover the clock.                                                                                                                                                                                                                             |  |

| Clock Recovery Damping<br>Factor | Sets the damping factor which is the value that used in designing the second order PLL to recover the clock. The damping factor and the 3 dB bandwidth of the PLL are related to the natural frequency using the following equation.                                                                        |  |

|                                  | $\omega_n = \frac{2\pi F_t}{\sqrt{2\zeta^2 - 1 + \sqrt{(2\zeta^2 - 1)^2 + 1}}}$                                                                                                                                                                                                                             |  |

|                                  | where:                                                                                                                                                                                                                                                                                                      |  |

|                                  | $\omega_n$ = the natural frequency of the PLL                                                                                                                                                                                                                                                               |  |

|                                  | $\zeta =$ the dampling factor of the PLL                                                                                                                                                                                                                                                                    |  |

|                                  | $F_t$ = the 3 dB bandwidth of the PLL                                                                                                                                                                                                                                                                       |  |

| Configurable Parameter Settin    | gs                                                                                                                                                                                                                                                                                                          |  |

| Bandwidth Reduction              | Specifies the bandwidth frequency for the oscilloscope. This configuration is only available when the Enhanced Bandwidth or Noise Reduction option is installed on the oscilloscope.                                                                                                                        |  |

| Vswing Edge                      | Sets the number of Edges used when performing the Vswing<br>measurement. The Vswing value is used to ensure that the waveform<br>is displayed as large as possible in the waveform viewing area.<br>Increasing this value increases the test run time but improves the<br>repeatability of the measurement. |  |

| VTop & VBase Edge                | Sets the number of edges required when making the VTop and VBase measurements.                                                                                                                                                                                                                              |  |

| Expert Mode                      | Turn on the expert mode for looser pre-requisite checker.                                                                                                                                                                                                                                                   |  |

| Test Plan Check Mode             | Turn on test plan check mode to simulate the actual test plan run flow without actual tests being run.                                                                                                                                                                                                      |  |

| SSC Acquisitions                 | Number of SSC cycle captured for SSC related tests. Maximum number is 25.                                                                                                                                                                                                                                   |  |

| Memory Depth                     | Sets the memory depth for acquisition                                                                                                                                                                                                                                                                       |  |

| PRBS Validation Algorithm Set    | ttings                                                                                                                                                                                                                                                                                                      |  |

| PRBS pattern checker rule        | Determine the rules applied to PRBS 7 Pattern detector. By selecting Strict, test can only proceed with the correct PRBS 7 pattern only.                                                                                                                                                                    |  |

|                                  | Source Differential Tests                                                                                                                                                                                                                                                                                   |  |

| Eye Diagram                      |                                                                                                                                                                                                                                                                                                             |  |

| Eye Diagram Edge                 | Sets the number of edges measured for the eye test.                                                                                                                                                                                                                                                         |  |

#### Table 1 Test Configuration Options

| Configuration Option         | Description                                                                                                                                                                                                                                                                                                   |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mask Scaling Option          | Sets the type of scaling performed on the mask for the eye test.                                                                                                                                                                                                                                              |

| Mask Type                    | Selects the type of mask to use for the eye test.                                                                                                                                                                                                                                                             |

| Eye Diagram Mask<br>Movement | This field contains 3 options. (1) Find Passing Mode will automatically search +/-0.5UI horizontally until no violation occurs, (2) Fixed Mask will not be moving, it only report Pass or Fail upon test, (3) Find Margin will search +/-0.5UI horizontally to find the maximum margin of non-violation mask. |

| CTS Version for Eye Mask     | Set the mask file to CTS version 1.0, 1.1, or 1.2                                                                                                                                                                                                                                                             |

#### **Test Condition**

Bit Rate: all bit rates are supported.

Output Level: 800 mVolts.

Pre-Emphasis: 0 dB (for CTS 1.1a and below), or set by the source such that the source will meet the Pass/Fail criteria (for CTS 1.2).

Test Pattern: PRBS 7 (for RBR and HBR), or 8b10b (for HBR2).

SSC: If the device under test is able to operate either with SSC Enabled or SSC Disabled then the device is tested for both conditions. If the device is always SSC Enabled or always SSC Disabled then the device is tested in its normal state.

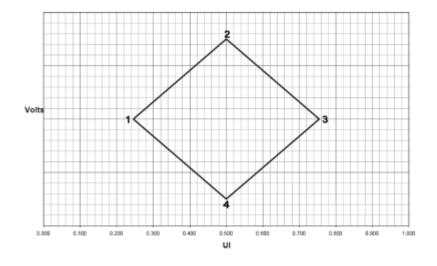

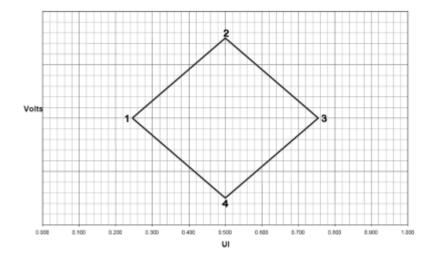

#### **PASS Condition**

The following table and figure define the mask for the eye measurements of CTS 1.1a and below. There can be no signal trajectories entering into the mask. Table 2 shows the voltage and time coordinates for the mask used in the eye diagram. The specification states that either 400mV, 600mV, or 800mV setting must pass.

|            | Bit Rate            |                 |

|------------|---------------------|-----------------|

| Mask Point | Reduced (1.62 Gb/s) | High (2.7 Gb/s) |

| 1          | 0.127, 0.000        | 0.210, 0.000    |

| 2          | 0.291, 0.160        | 0.355, 0.140    |

| 3          | 0.500, 0.200        | 0.500, 0.175    |

| 4          | 0.709, 0.200        | 0.645, 0.175    |

| 5          | 0.875, 0.000        | 0.790, 0.000    |

| 6          | 0.709,-0.200        | 0.645,-0.175    |

| 7          | 0.500,-0.200        | 0.500,-0.175    |

| 8          | 0.291,-0.160        | 0.355,-0.140    |

Table 2

Eye Diagram Mask Coordinates

Figure 10 The Source Eye Pattern Mask

Mask Test: Zero mask failures.

For CTS 1.2 eye measurements, there can be no signal trajectories entering the mask area as defined by the following:

Waveform Eye Height: Minimum 124mV

Waveform Eye Width: > .42 UI

The mask is aligned horizontally to the point where the maximum eye height occurs between 0.375UI - 0.625UI. The mask is aligned vertically around 0V differential.

## **Test References**

See Test 3.1: Eye Diagram Testing, in the *DisplayPort-Compliance Test* Specification Version 1.2 draft8 and Test 3.1: Eye Diagram Testing, in the DisplayPort-Compliance Test Specification Version 1.1a.

# Source Eye Diagram Differential Tests

4

U7232B DisplayPort Electrical Performance Compliance Test Application Method of Implementation

# **Source Total Jitter Differential Tests**

Probing for Source Total Jitter Differential Tests 40 Source Total Jitter Differential Tests 42

This section provides the guidelines for source total jitter differential tests using an Agilent Infiniium oscilloscope, InfiniiMax probes, and the DisplayPort Electrical Performance Compliance Test Application.

#### 4 Source Total Jitter Differential Tests

# **Probing for Source Total Jitter Differential Tests**

When performing the source total jitter test, the DisplayPort Electrical Performance Compliance Test Application will prompt you to make the proper connections. Your DisplayPort test environment setup on the Set Up tab must match the physical connection.

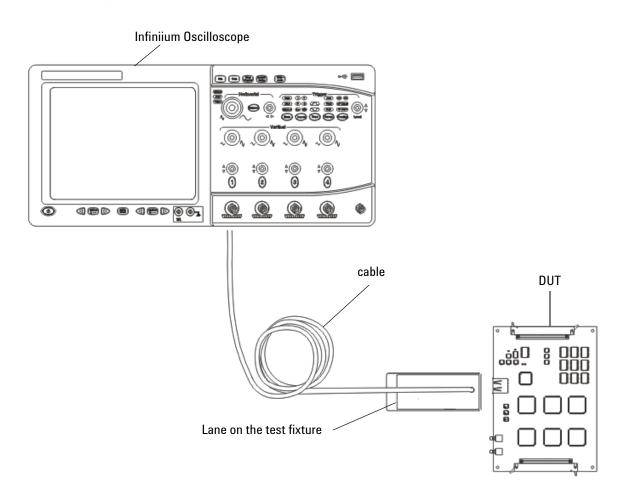

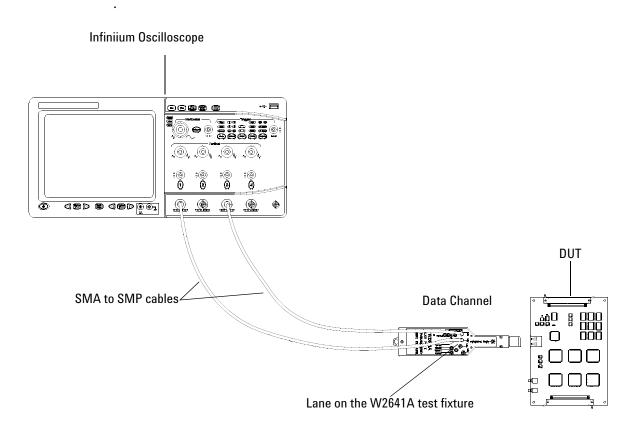

Figure 11 and Figure 12 show a physical connection for making differential and single-ended connections.

**Figure 11** Probing for Differential Tests - Total Jitter Tests (Single Connection with W2641A DisplayPort Test Fixture)

**Figure 12** Differential Measurement Setup Using Two Single Ended Connections - Total Jitter Tests (A Minus B Configuration)

You can use any oscilloscope channel and connect it to any lane test point. You select the channels used for testing lanes in the Set Up tab of the DisplayPort Electrical Performance Compliance Test Application.

The data lanes and channels shown in the previous figures are just examples. You can choose any desired data lane and channel that you want.

# **Source Total Jitter Differential Tests**

To evaluate the total jitter accompanying the data transmission at either an explicit bit error rate of  $10^{-9}$  or through an approved estimation technique. This measurement is a data time interval error (Data-TIE) jitter measurement. (Reference: Table 3.13 VESA DisplayPort Standard).

The overall system jitter budget allocates different amounts of jitter which each component of the system is allowed to contribute. To exceed any of these limits is to violate the component level jitter budget. (Reference: Jitter model in base DisplayPort Specification (Section 3.5.3.9: The Dual Dirac Jitter Model)).

For Compliance Test Specifications 1.1a and below, the test must use a PRBS 7 test pattern at all voltage levels. For Compliance Test Specifications 1.2, the test must use an 8b10b or a D10.2 test pattern. The test can be performed with pre-Emphasis for best performance results.

## **Test Procedure**

- 1 Start the automated testing application as described in "Starting the DisplayPort Electrical Performance Compliance Test Application" on page 24.

- **2** Connect the W2641A test fixture or other appropriate fixture to the device under test (DUT).

- **3** If you are using one connection, connect the probe to one channel. If you are using two connections, connect the two probes to two channels of the oscilloscope. If you are using four connections, connect the four probes to four channels of the oscilloscope.

- **4** Connect the SMA to SMP cable to the SMA probe head of one of the probes and to the data lane connector on the W2641A fixture that you want to test.

- 5 Connect the other SMA to SMP cable to the other SMA probe head and to the data lane on the W2641A test fixture that you want to test.

- 6 In the DisplayPort Compliance Test Application, click the Set Up tab.

- 7 Set the Device ID, Operator ID, Project ID, Test Type, DUT Definition Settings, Fixture Type, Connection Type and Number of Channels according to the type of testing being done.

| DisplayPor              | rt DisplayPort 1 *                                                                              |     |

|-------------------------|-------------------------------------------------------------------------------------------------|-----|

| File View               | Help                                                                                            |     |

| D 📽 🖬 🔤                 | M 1 L   @ @ 0                                                                                   |     |

| Task Flow               | Set Up Select Tests Configure Connect Run Tests Results Html Report                             |     |

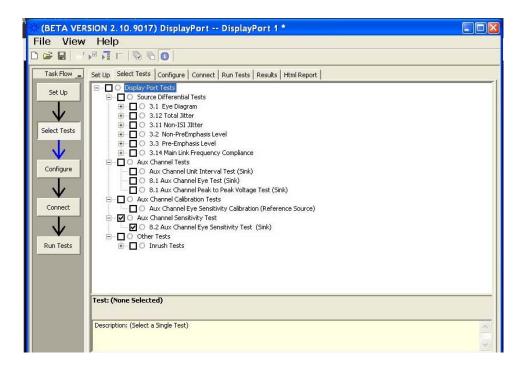

| Set Up                  | Display Port Tests     Display Port Tests     O Source Differential Tests     O 3.1 Eye Diagram | ^   |

| Select Tests            | <ul> <li>3.12 Total Jitter</li> <li>Lane 0 - Total Jitter Test</li> </ul>                       |     |

|                         | Lane 1 - Total Jitter Test<br>Lane 2 - Total Jitter Test<br>Lane 3 - Total Jitter Test          |     |

| Configure               |                                                                                                 |     |

|                         | O 3.8 Overshoot Test      O 3.3 Pre-Emphasis Level      O 3.4 Teter Dein Clement                | ~   |

| $\overline{\mathbf{v}}$ | Test: (None Selected)                                                                           |     |

| Run Tests               | Description: (Select a Single Test)                                                             | < > |

| 2 Tests Check           | <pre>k the test(s) you would like to run</pre> Connection: UNKNOWN                              |     |

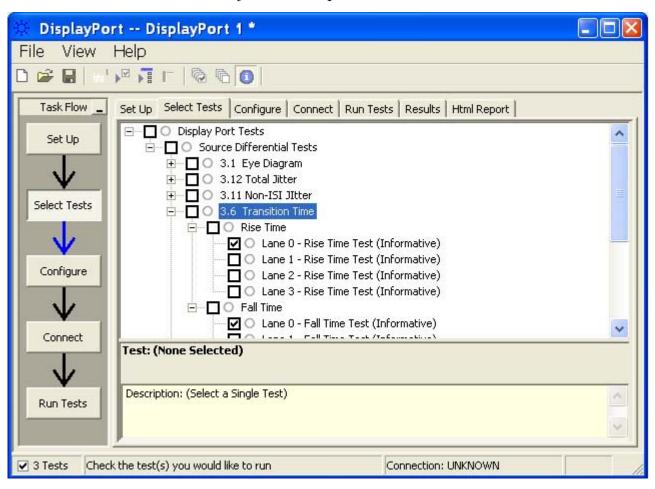

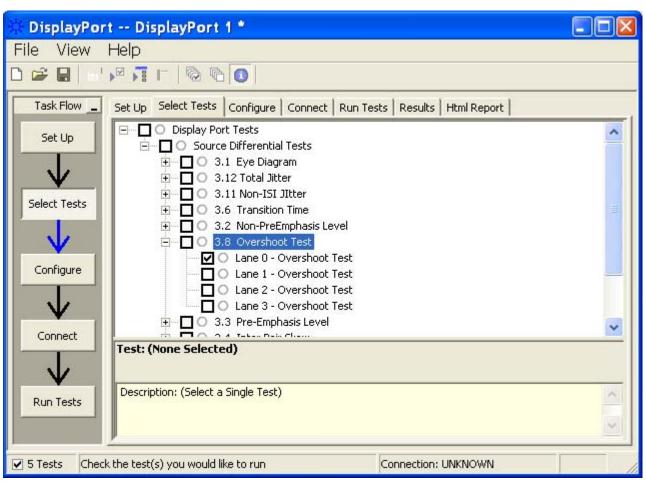

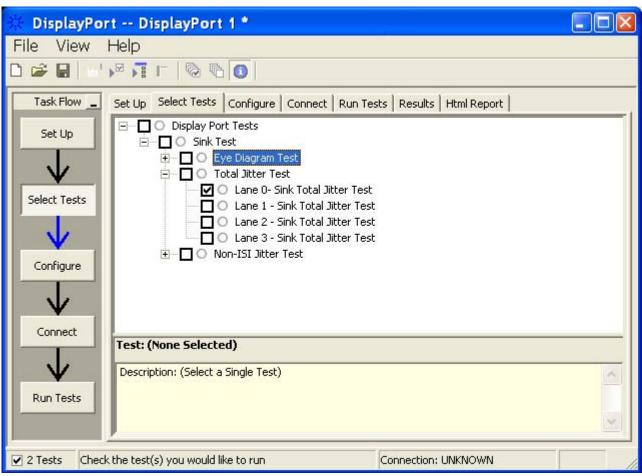

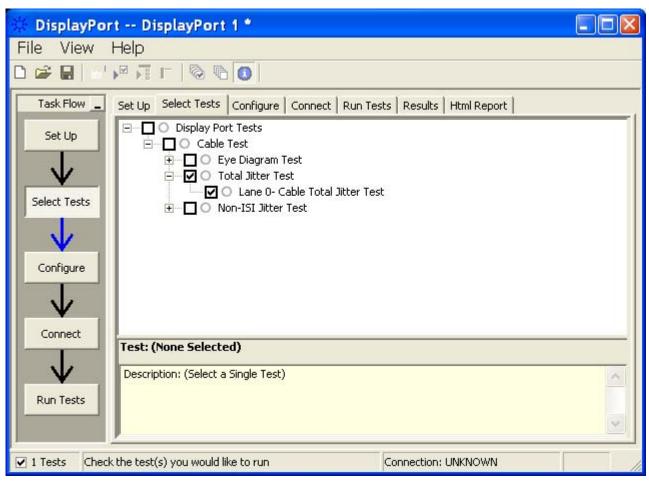

Navigate to the Total Jitter - Lane # - where # is the lane number to be tested.

Figure 13 Selecting Source Total Jitter Differential Tests

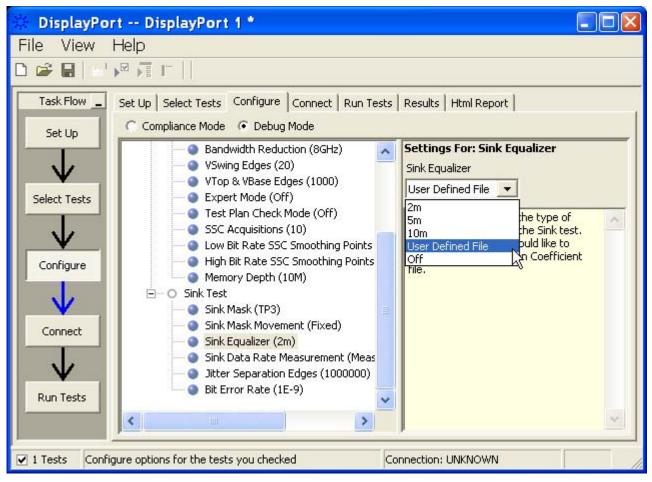

8 Follow the DisplayPort Electrical Performance Compliance Test Application's task flow to set up configuration options (see Table 3), run the test and view the test results. Options may vary depending on selected mode: Compliance Mode or Debug Mode.

### **4** Source Total Jitter Differential Tests

## Table 3 Test Configuration Options

| Configuration Option             | Description                                                                                                                                                                                                                                                                                                 |  |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Clock Recovery Settings          |                                                                                                                                                                                                                                                                                                             |  |

| Clock Recovery Order             | Set either a second order PLL or a first order PLL method to recover the clock.                                                                                                                                                                                                                             |  |

| Clock Recovery Damping<br>Factor | Sets the damping factor which is the value that used in designing the second order PLL to recover the clock. The damping factor and the 3 dB bandwidth of the PLL are related to the natural frequency using the following equation.                                                                        |  |

|                                  | $\omega = \frac{2\pi F_t}{1}$                                                                                                                                                                                                                                                                               |  |

|                                  | $\omega_n = \frac{2\pi F_t}{\sqrt{2\zeta^2 - 1 + \sqrt{(2\zeta^2 - 1)^2 + 1}}}$                                                                                                                                                                                                                             |  |

|                                  | where:                                                                                                                                                                                                                                                                                                      |  |

|                                  | $\omega_n$ = the natural frequency of the PLL                                                                                                                                                                                                                                                               |  |

|                                  | $\zeta$ = the dampling factor of the PLL                                                                                                                                                                                                                                                                    |  |

|                                  | $F_t$ = the 3 dB bandwidth of the PLL                                                                                                                                                                                                                                                                       |  |

| Configurable Parameter Settin    | gs                                                                                                                                                                                                                                                                                                          |  |

| Bandwidth Reduction              | Specifies the bandwidth frequency for the oscilloscope. This configuration is only available when the Enhanced Bandwidth or Noise Reduction option is installed on the oscilloscope.                                                                                                                        |  |

| Vswing Edge                      | Sets the number of Edges used when performing the Vswing<br>measurement. The Vswing value is used to ensure that the waveform<br>is displayed as large as possible in the waveform viewing area.<br>Increasing this value increases the test run time but improves the<br>repeatability of the measurement. |  |

| VTop & VBase Edge                | Sets the number of edges required when making the VTop and VBase measurements.                                                                                                                                                                                                                              |  |

| Expert Mode                      | Turn on the expert mode for looser pre-requisite checker.                                                                                                                                                                                                                                                   |  |

| Test Plan Check Mode             | Turn on test plan check mode to simulate the actual test plan run flow without actual tests being run.                                                                                                                                                                                                      |  |

| SSC Acquisitions                 | Number of SSC cycle captured for SSC related tests. Maximum number is 25.                                                                                                                                                                                                                                   |  |

| Memory Depth                     | Sets the memory depth for acquisition                                                                                                                                                                                                                                                                       |  |

| PRBS Validation Algorithm Se     | ttings                                                                                                                                                                                                                                                                                                      |  |

| PRBS pattern checker rule        | Determine the rules applied to PRBS 7 Pattern detector. By selecting Strict, test can only proceed with the correct PRBS 7 pattern only.                                                                                                                                                                    |  |

|                                  | Source Differential Tests                                                                                                                                                                                                                                                                                   |  |

| Jitter Separation Settings       |                                                                                                                                                                                                                                                                                                             |  |

| Jitter Separation Edges          | Sets the number of edges measured for the jitter separation test.                                                                                                                                                                                                                                           |  |

#### Table 3 Test Configuration Options

| Configuration Option | Description                                         |

|----------------------|-----------------------------------------------------|

| Bit Error rate       | Sets the bit error rate for the RJ/DJ measurements. |

## **Test Condition**

Bit Rate: all bit rates are supported (for CTS 1.1a and below), or 5.4Gbps (for CTS 1.2).

Output Level: all output levels are supported (for CTS 1.1a and below), or user-defined (for CTS 1.2).

Pre-Emphasis: 0 dB (for CTS 1.1a and below), or user-defined (for CTS 1.2).

Test Pattern: PRBS 7 (for RBR and HBR), or 8b10b and D10.2 (for HBR2).

SSC: If the device under test is able to operate either with SSC Enabled or SSC Disabled then the device is tested for both conditions. If the device is always SSC Enabled or always SSC Disabled then the device is tested in its normal state.

### **PASS Condition**

**Table 4**Total Jitter at Internal and Compliance Points (CTS 1.1a).

|                                   | Transmitter Connector (TP2) |

|-----------------------------------|-----------------------------|

| High-bit Rate (2.7 Gb/s per lane) |                             |

| A <sub>p-p</sub>                  | 0.420 UI                    |

| Reduced-bit                       | Rate (1.62 Gb/s per lane)   |

| A <sub>p-p</sub>                  | 0.270 UI                    |

Table 5

Total Jitter at Internal and Compliance Points (CTS 1.2).

| High-bit Rate (2.7 Gb/s per lane) |  |

|-----------------------------------|--|

|                                   |  |

|                                   |  |

|                                   |  |

|                                   |  |

| Receiver Connector (TP3_EQ)         |           |           |  |

|-------------------------------------|-----------|-----------|--|

| High-bit Rate 2 (5.4 Gb/s per lane) |           |           |  |

|                                     | 8b10b     | D10.2     |  |

| A <sub>p-p</sub>                    | < 0.62 UI | < 0.40 UI |  |

UI is Unit Interval.

## **Test References**

See Test 3.1: Eye Diagram Testing, in the DisplayPort-Compliance Test Specification Version 1.2 draft8 and Test 3.1: Eye Diagram Testing, in the DisplayPort-Compliance Test Specification Version 1.1a.

5

U7232B DisplayPort Electrical Performance Compliance Test Application Method of Implementation

# **Source Non-ISI Jitter Differential Tests**

Probing for Source Non-ISI Jitter Differential Tests 48 Source Non-ISI Jitter Differential Tests 50

This section provides the guidelines for source non-ISI jitter differential tests using an Agilent 8 GHz or greater Infiniium oscilloscope, InfiniiMax probes, and the DisplayPort Electrical Performance Compliance Test Application.

#### **5** Source Non-ISI Jitter Differential Tests

# **Probing for Source Non-ISI Jitter Differential Tests**

When performing the non-ISI jitter test, the DisplayPort Electrical Performance Compliance Test Application will prompt you to make the proper connections. Your DisplayPort test environment setup on the Set Up tab must match the physical connection.

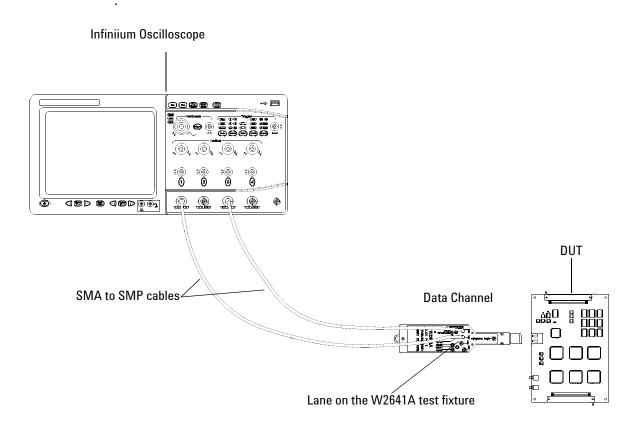

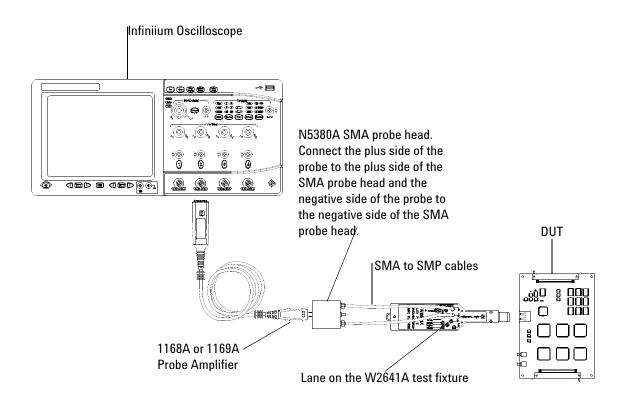

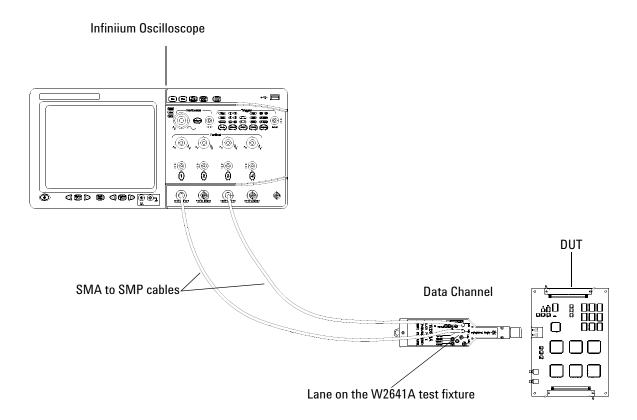

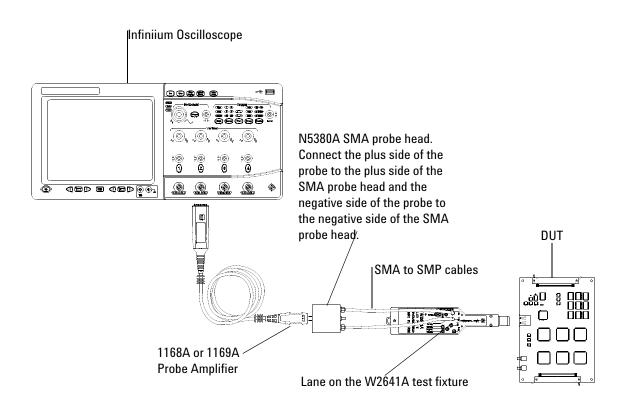

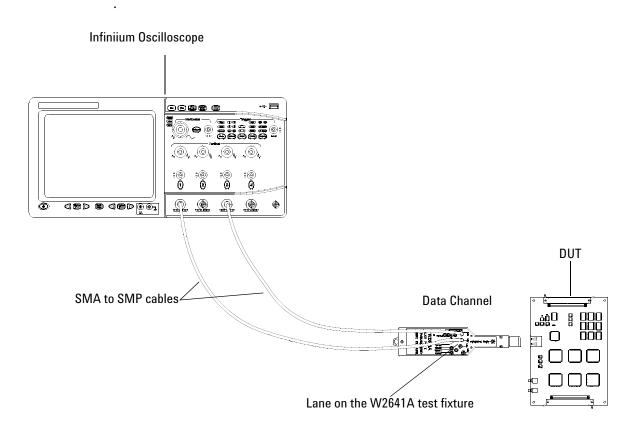

Figure 14 and Figure 15 show a physical connection for making differential and single-ended connections.

**Figure 14** Probing for Differential Tests - Non-ISI Jitter Tests (Single Connection with W2641A DisplayPort Test Fixture)

**Figure 15** Differential Measurement Setup Using Two Single Ended Connections - Non-ISI Jitter Tests (A Minus B Configuration)

You can use any oscilloscope channel and connect it to any lane test point. You select the channels used for testing lanes in the Set Up tab of the DisplayPort Electrical Performance Compliance Test Application.

The data lanes and channels shown in the previous figures are just examples. You can choose any desired data lane and channel that you want.

# Source Non-ISI Jitter Differential Tests

To evaluate the Non-ISI jitter accompanying the data transmission at either an explicit bit error rate of  $10^{-9}$  or through an approved estimation technique. (Reference: Table 3.13 VESA DisplayPort Standard).

The overall system jitter budget allocates different amounts of jitter which each component of the system is allowed to contribute. To exceed any of these limits is to violate the component level jitter budget. (Reference: Jitter model in base DisplayPort Specification (Section 3.5.3.9: The Dual Dirac Jitter Model)).

The test must use a PRBS 7 test pattern at all voltage levels. The test can be performed with pre-Emphasis for best performance results.

## **Test Procedure**

- 1 Start the automated testing application as described in "Starting the DisplayPort Electrical Performance Compliance Test Application" on page 24.

- **2** Connect the W2641A test fixture or other appropriate fixture to the device under test (DUT).

- **3** If you are using one connection, connect the probe to one channel. If you are using two connections, connect the two probes to two channels of the oscilloscope. If you are using four connections, connect the four probes to four channels of the oscilloscope.

- **4** Connect the SMA to SMP cable to the SMA probe head of one of the probes and to the data lane connector on the W2641A fixture that you want to test.

- 5 Connect the other SMA to SMP cable to the other SMA probe head and to the data lane on the W2641A test fixture that you want to test.

- 6 In the DisplayPort Compliance Test Application, click the Set Up tab.

- 7 Set the Device ID, Operator ID, Project ID, Test Type, DUT Definition Settings, Fixture Type, Connection Type and Number of Channels according to the type of testing being done.

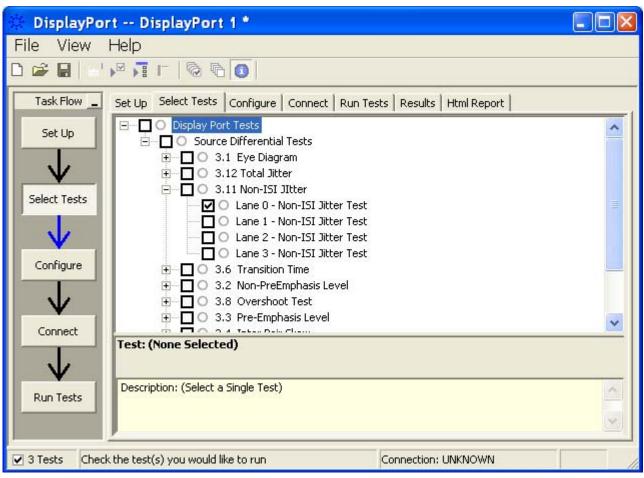

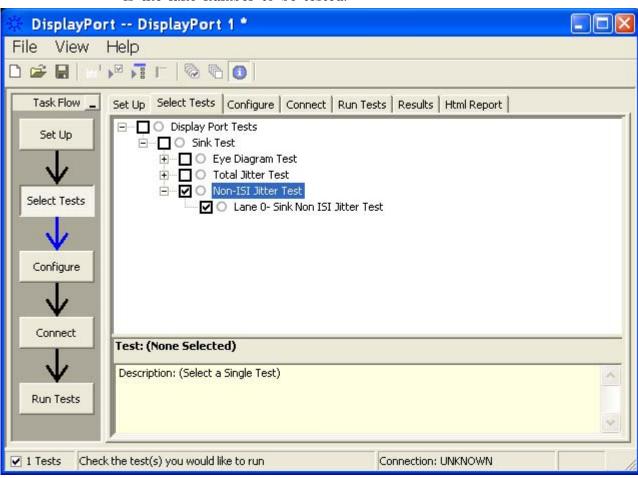

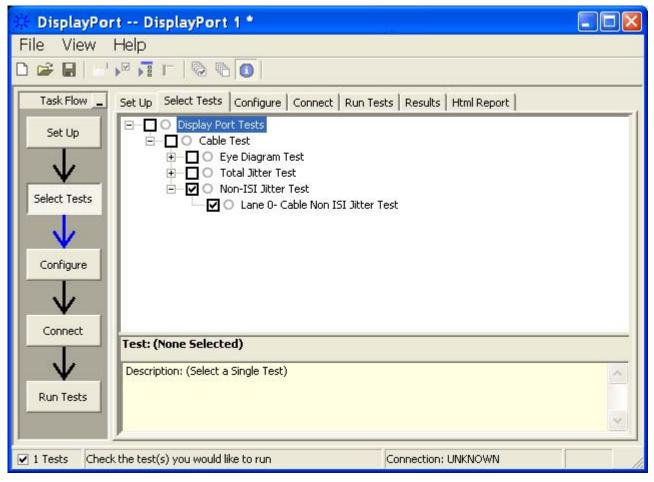

Navigate to the Non-ISI Jitter - Lane # - Non-ISI Jitter Test where # is the lane number to be tested.

Figure 16 Selecting Source Non-Jitter Differential Tests

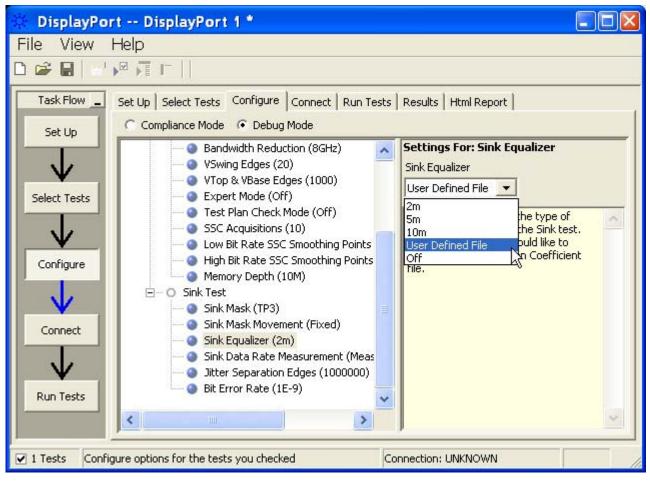

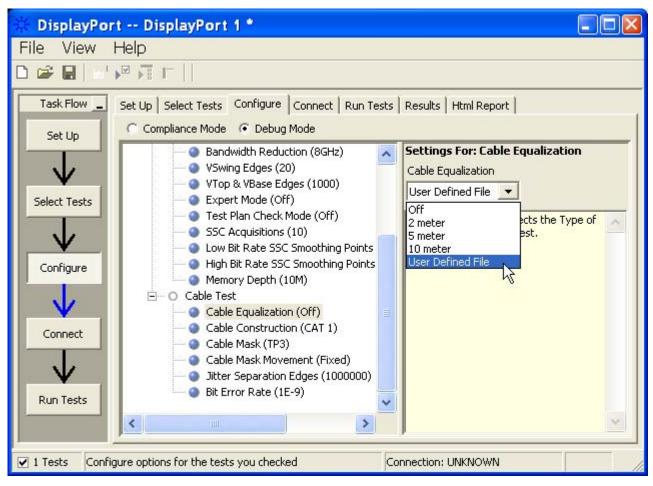

8 Follow the DisplayPort Electrical Performance Compliance Test Application's task flow to set up configuration options (see Table 6), run the test and view the test results. Options may vary depending on selected mode: Compliance Mode or Debug Mode.

## **5** Source Non-ISI Jitter Differential Tests

## Table 6 Test Configuration Options

| Configuration Option             | Description                                                                                                                                                                                                                                                                                                 |  |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Clock Recovery Settings          |                                                                                                                                                                                                                                                                                                             |  |

| Clock Recovery Order             | Set either a second order PLL or a first order PLL method to recover the clock.                                                                                                                                                                                                                             |  |

| Clock Recovery Damping<br>Factor | Sets the damping factor which is the value that used in designing the second order PLL to recover the clock. The damping factor and the 3 dB bandwidth of the PLL are related to the natural frequency using the following equation.                                                                        |  |

|                                  | $\omega_n = \frac{2\pi F_t}{\sqrt{2\zeta^2 - 1 + \sqrt{(2\zeta^2 - 1)^2 + 1}}}$                                                                                                                                                                                                                             |  |

|                                  | where:                                                                                                                                                                                                                                                                                                      |  |

|                                  | $\omega_n$ = the natural frequency of the PLL                                                                                                                                                                                                                                                               |  |

|                                  | $\zeta =$ the dampling factor of the PLL                                                                                                                                                                                                                                                                    |  |

|                                  | $F_t$ = the 3 dB bandwidth of the PLL                                                                                                                                                                                                                                                                       |  |

| Configurable Parameter Settin    | gs                                                                                                                                                                                                                                                                                                          |  |

| Bandwidth Reduction              | Specifies the bandwidth frequency for the oscilloscope. This configuration is only available when the Enhanced Bandwidth or Noise Reduction option is installed on the oscilloscope.                                                                                                                        |  |

| Vswing Edge                      | Sets the number of Edges used when performing the Vswing<br>measurement. The Vswing value is used to ensure that the waveform<br>is displayed as large as possible in the waveform viewing area.<br>Increasing this value increases the test run time but improves the<br>repeatability of the measurement. |  |

| VTop & VBase Edge                | Sets the number of edges required when making the VTop and VBase measurements.                                                                                                                                                                                                                              |  |

| Expert Mode                      | Turn on the expert mode for looser pre-requisite checker.                                                                                                                                                                                                                                                   |  |

| Test Plan Check Mode             | Turn on test plan check mode to simulate the actual test plan run flow without actual tests being run.                                                                                                                                                                                                      |  |

| SSC Acquisitions                 | Number of SSC cycle captured for SSC related tests. Maximum number is 25.                                                                                                                                                                                                                                   |  |

| Memory Depth                     | Sets the memory depth for acquisition                                                                                                                                                                                                                                                                       |  |

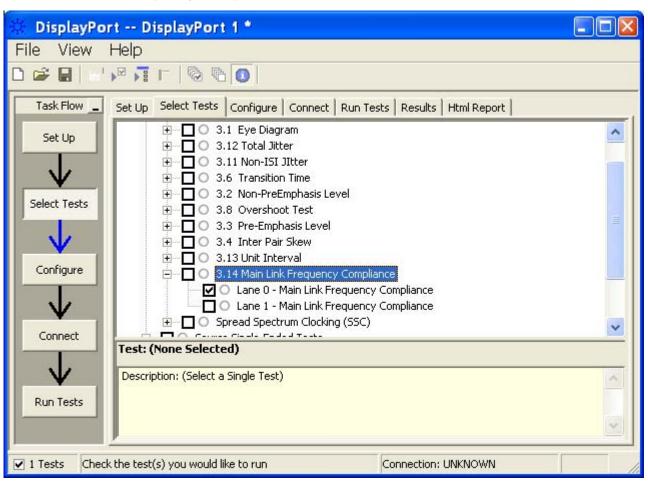

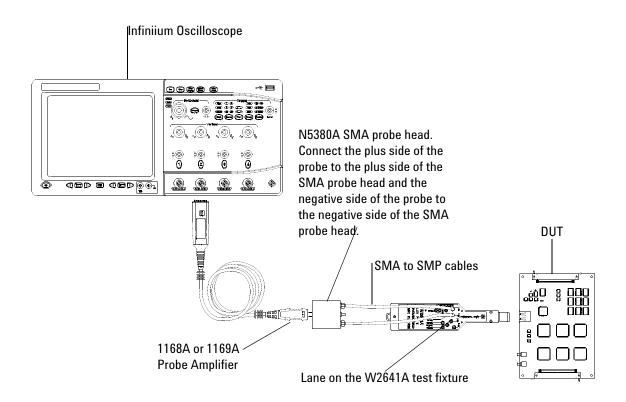

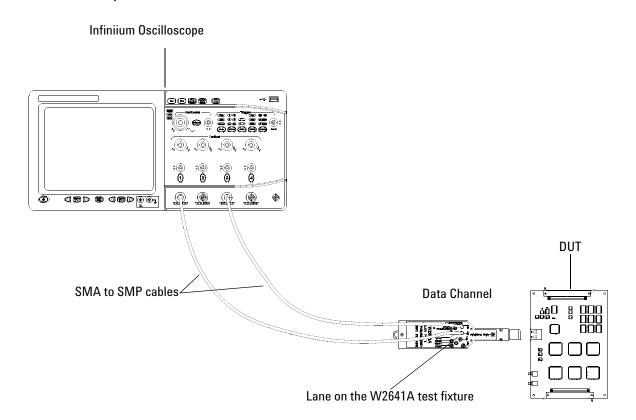

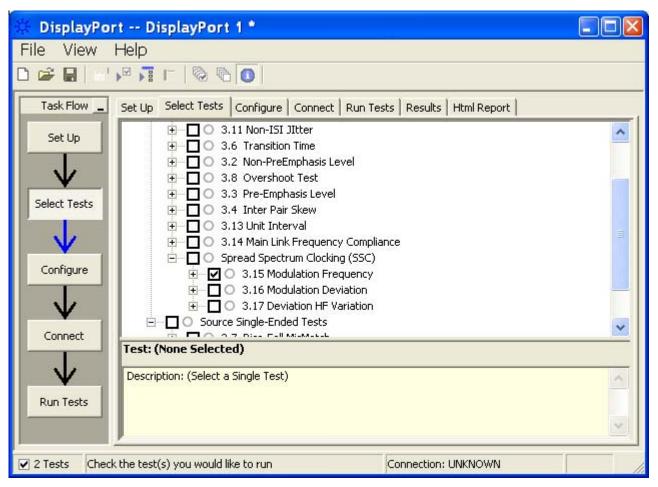

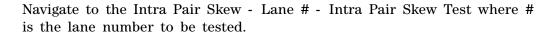

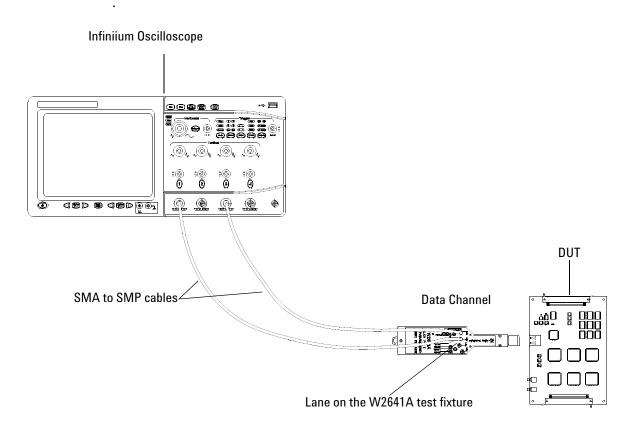

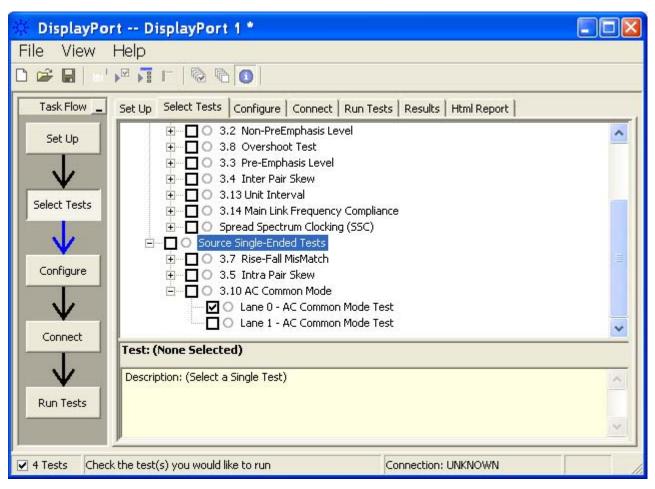

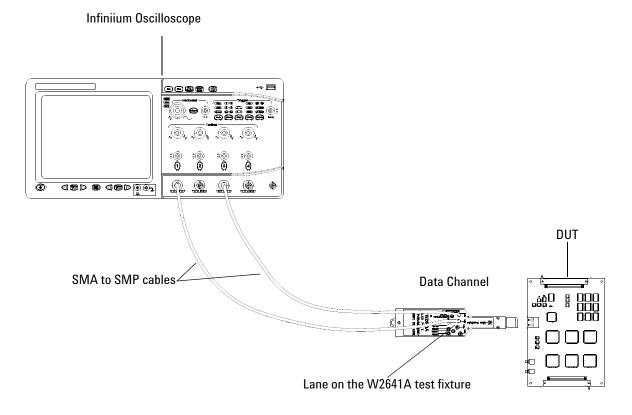

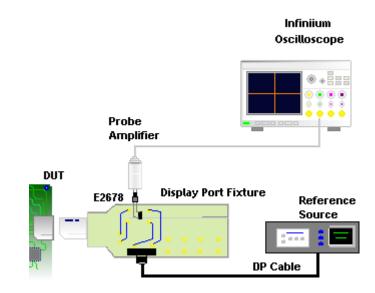

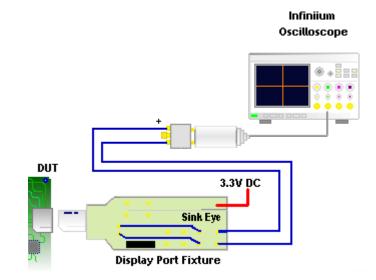

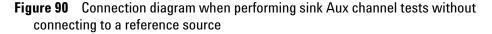

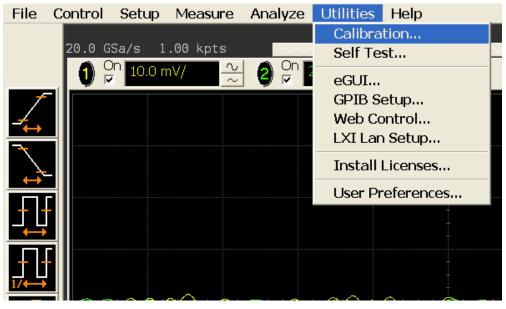

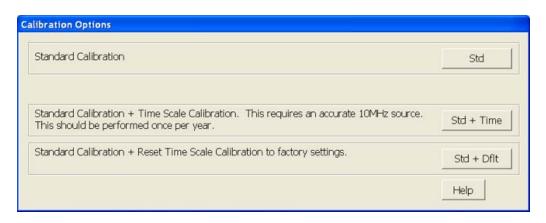

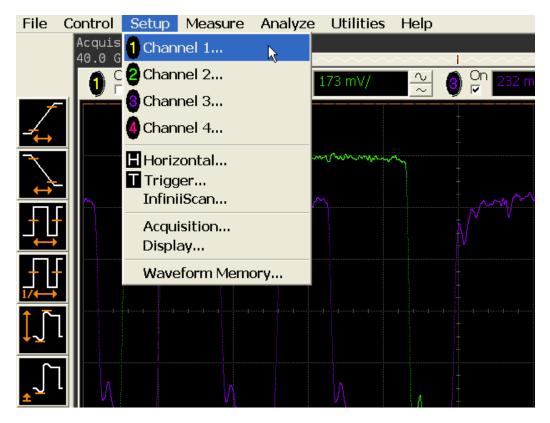

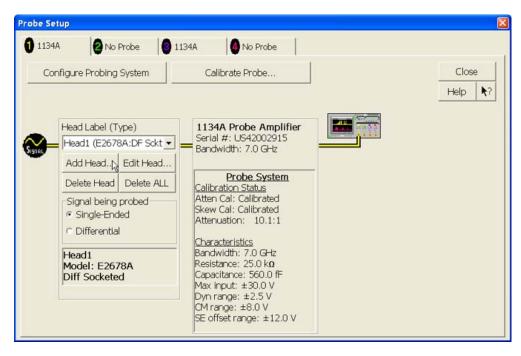

| RBS Validation Algorithm Se      | ttings                                                                                                                                                                                                                                                                                                      |  |